Встроенный дизайн с FPGA:создание проекта

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

1:аппаратные ресурсы

2:языки реализации

3:Процесс разработки

4:Создание проекта (эта статья)

5:реализация

Адаптировано из книги Джима Ледина "Архитектура высокопроизводительных встраиваемых систем".

Разработка вашего первого проекта FPGA

В этом разделе мы разработаем и реализуем простой, но законченный проект с использованием устройства FPGA Xilinx Artix-7, установленного на плате разработки Digilent Arty A7. Эта плата поставляется в двух вариантах:более дешевая версия (129 долларов США) с номером модели, оканчивающимся на -35T, и более функциональная, но более дорогая версия (249 долларов США) с номером модели, заканчивающимся на -100T. Единственное различие между двумя платами - это модель установленной на плате ПЛИС Artix-7. Как и следовало ожидать, у -35T меньше доступных ресурсов, чем у -100T.

Вы можете использовать для этого проекта вариант -35T или -100T. Единственная разница в процессе разработки - это определение правильной модели платы всякий раз, когда возникает необходимость. Однако в следующих главах потребуется вариант -100T из-за требований к ресурсам, связанных с проектом цифрового осциллографа, поэтому рекомендуется использовать более мощную плату.

Платы Arty A7 доступны для покупки на https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ и из других источников, таких как Amazon.

Для целей этого проекта интересующие нас ресурсы на плате - это само устройство FPGA, а также четыре переключателя, четыре кнопки и пять светодиодов. Этот проект продемонстрирует, как установить набор инструментов Vivado, создать проект, ввести код HDL, протестировать код и, в конечном итоге, создать поток битов и загрузить его на плату. После загрузки битового потока на плату вы сможете вручную протестировать работу системы. Вы также узнаете, как запрограммировать образ ПЛИС во флэш-память на плате Arty A7, чтобы он загружался и запускался при каждом включении платы.

Установка инструментов Vivado

Мы будем использовать набор инструментов разработки ПЛИС Xilinx Vivado для этого проекта и для проектов в будущих главах. Эти инструменты доступны бесплатно и поддерживаются в операционных системах Windows и Linux. Вы можете установить инструменты в любой из операционных систем. Описание в этом разделе касается версии инструментов для Windows, но если вы устанавливаете в Linux, различия должны быть очевидны. Работа с инструментами Vivado должна быть почти одинаковой в разных операционных системах:

- Если у вас его еще нет, создайте учетную запись пользователя Xilinx на странице https://www.xilinx.com/registration/create-account.html.

- Посетите https://xilinx.com и войдите в свою учетную запись. После входа в систему перейдите на страницу загрузки инструментов по адресу https://www.xilinx.com/support/download.html.

- Загрузите Унифицированный установщик Xilinx:самораспаковывающийся веб-установщик Windows . . Вероятно, вам следует выбрать последнюю доступную версию, но если вы хотите следовать вместе с версией, используемой в этой книге, выберите версию 2020.1 .

- Имя установочного файла будет похоже на Xilinx_ 1_0602_1208_Win64.exe. Найдите этот файл в каталоге загрузок и запустите. Если появится диалоговое окно с предупреждением об установке приложения, не подтвержденного корпорацией Майкрософт, нажмите Все равно установить . .

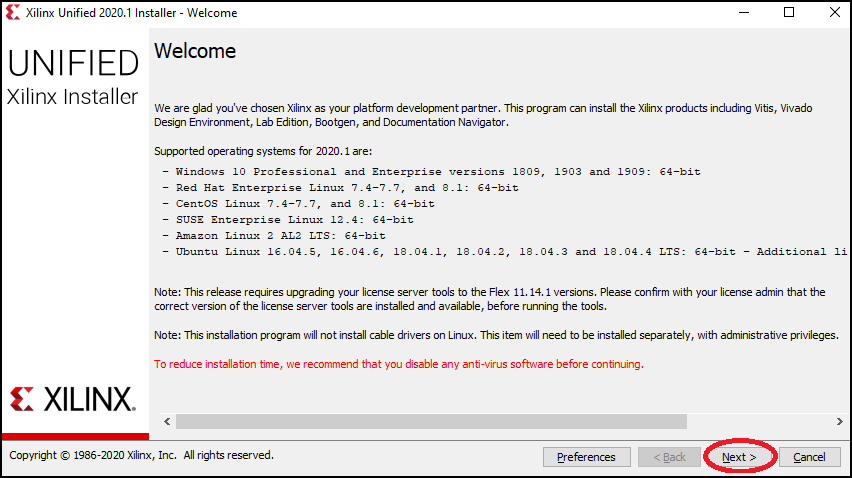

- Когда Добро пожаловать появится экран, нажмите Далее :

Рисунок 4.3 - Диалоговое окно с приветствием установщика

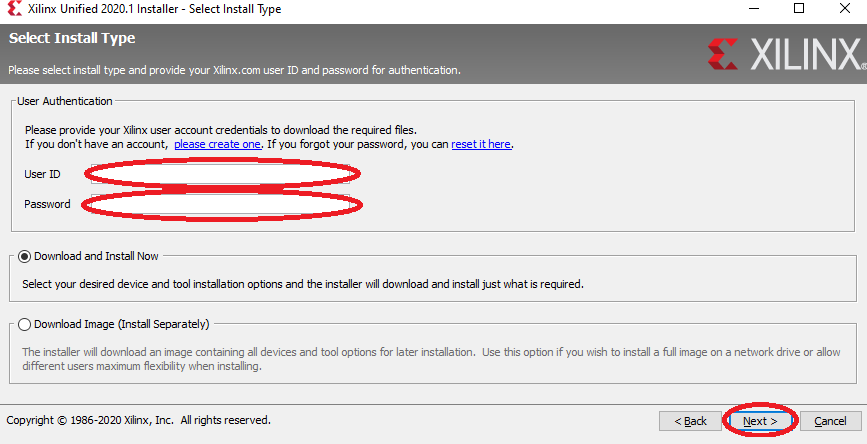

- На следующем экране введите свой идентификатор пользователя xilinx.com и пароль, затем нажмите Далее . :

Рисунок 4.4 - Диалог входа в программу установки

- В следующем диалоговом окне вам будет предложено принять некоторые лицензионные соглашения. Установите флажки Принимаю . , затем нажмите Далее .

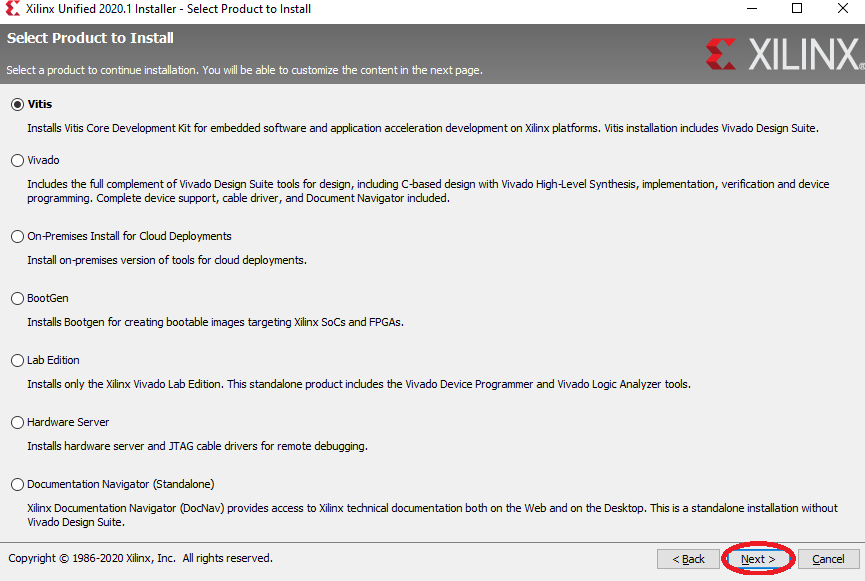

- В следующем диалоговом окне оставьте Vitis . выбран в качестве продукта для установки и нажмите Далее . Vitis включает набор инструментов Vivado вместе с набором других инструментов разработки Xilinx:

Рисунок 4.5 - Диалоговое окно выбора продукта установщика

- В следующем диалоговом окне можно выбрать компоненты программного обеспечения для установки. Оставьте для выбора значения по умолчанию и нажмите Далее . .

- В следующем диалоговом окне вы можете выбрать целевой каталог и указать параметры ярлыка программы. Целевой каталог C:\ Xilinx является подходящим местом. Создайте этот каталог, если он не существует. Нажмите Далее . .

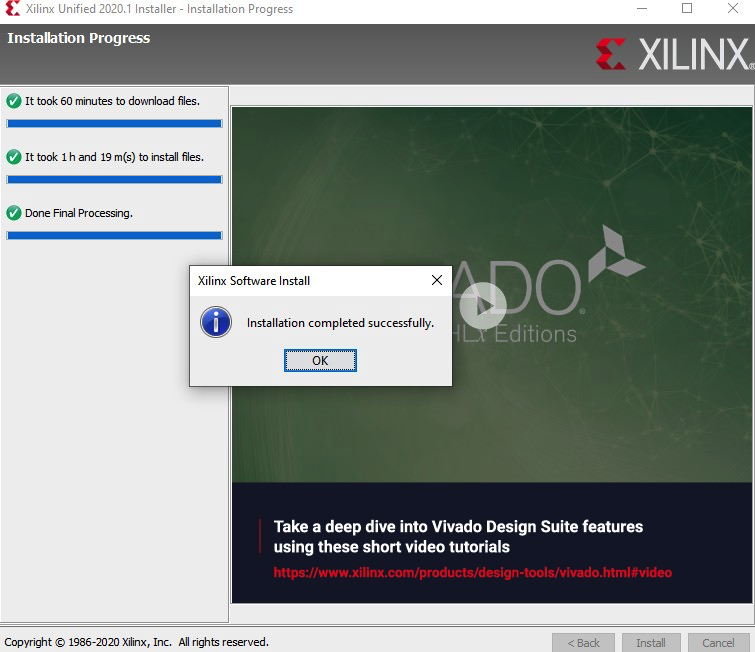

- В следующем диалоговом окне отображается сводка параметров установки. Нажмите Установить . чтобы продолжить установку. В зависимости от скорости вашего компьютера и вашего интернет-соединения установка может занять несколько часов:

Рисунок 4.6 - Диалоговое окно завершения установки

После завершения установки мы создадим наш первый проект.

Создание проекта

Выполните следующие действия, чтобы создать и собрать проект 4-битного двоичного сумматора для платы Arty A7:

- Найдите на рабочем столе значок под названием Vivado 2020.1 . (или найдите номер своей версии, если он другой) и дважды щелкните по нему.

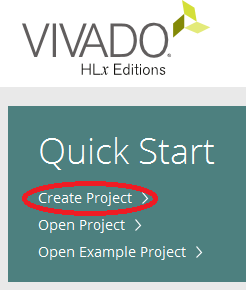

- Когда Vivado отобразит свой главный экран, нажмите Создать проект . в Быстрый запуск раздел:

Рисунок 4.7 - Диалоговое окно быстрого запуска Vivado

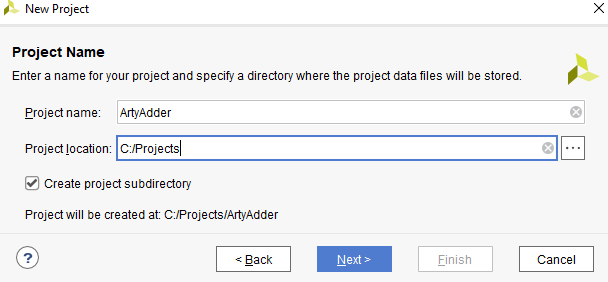

- Запустится Создание нового проекта Vivado . волшебник. Нажмите Далее . чтобы перейти к названию проекта страницу и введите ArtyAdder в качестве имени проекта. Выберите соответствующий каталог для проекта и установите флажок, чтобы создать подкаталог, затем нажмите Далее . . В примерах в этой книге каталог C:\ Projects будет использоваться в качестве местоположения для всех проектов:

Рисунок 4.8 - Диалоговое окно "Название проекта"

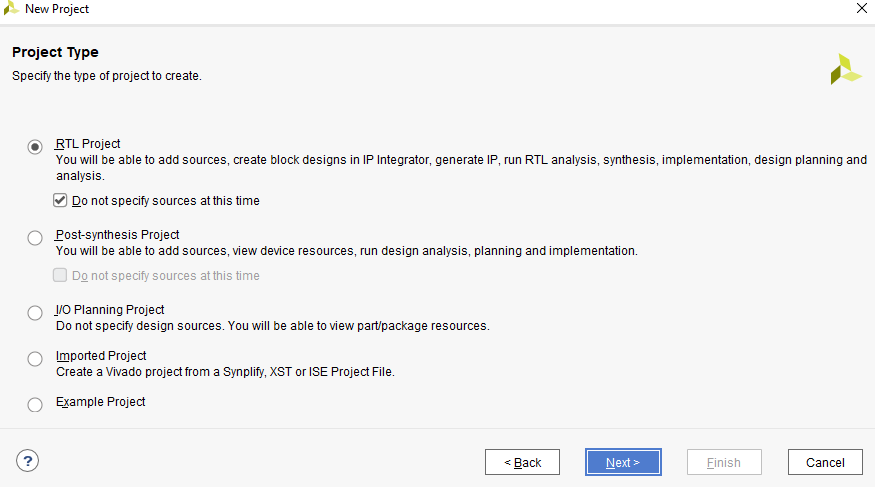

- В Типе проекта в диалоговом окне выберите Проект RTL . и установите флажок рядом с Не указывать источники в настоящее время . Нажмите Далее . :

Рисунок 4.9 - Диалоговое окно "Тип проекта"

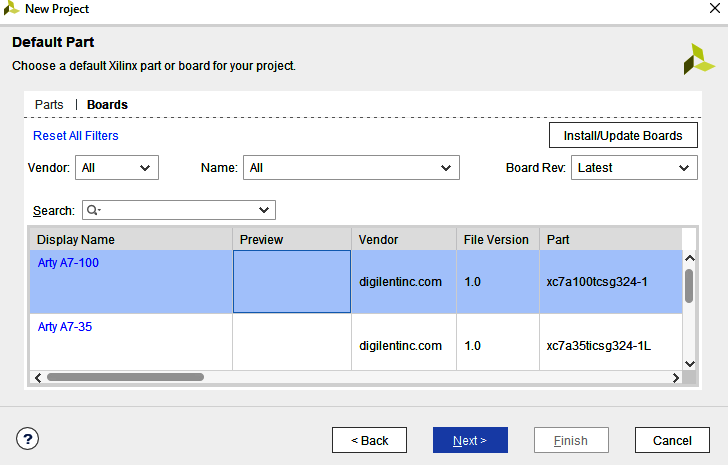

- В части по умолчанию диалоговом окне нажмите Доски вкладка и введите Arty в Поиск поле. В зависимости от типа вашей платы (или если у вас ее еще нет) выберите либо Arty A7-100 . или Arty A7-35 и нажмите Далее :

Рисунок 4.10 - Диалоговое окно "Деталь по умолчанию"

- В Сводке нового проекта диалоговом окне нажмите Готово .

Мы создали пустой проект. В следующем разделе мы создадим исходные файлы VHDL, содержащие схему логической схемы для этого проекта.

Создание исходных файлов VHDL

Следующие шаги описывают процесс создания исходных файлов VHDL, ввода исходного кода и компиляции проекта FPGA:

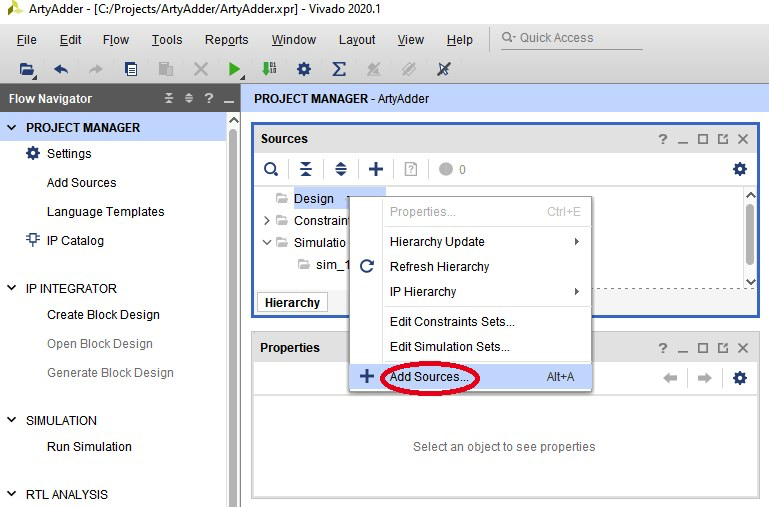

- В разделе Источники в дополнительном окне щелкните правой кнопкой мыши Источники дизайна . и выберите Добавить источники… :

Рисунок 4.11. Пункт меню «Добавить источники…»

- В Добавить источники в диалоговом окне убедитесь, что Добавить или создать источники дизайна выбран, затем нажмите Далее .

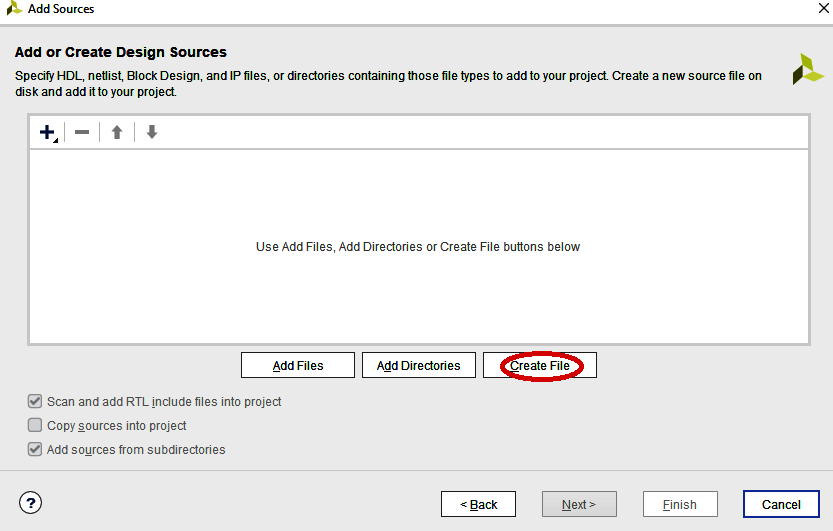

- В Добавить или создать источники дизайна в диалоговом окне нажмите Создать файл . :

Рисунок 4.12. Диалоговое окно "Добавить или создать исходный код проекта"

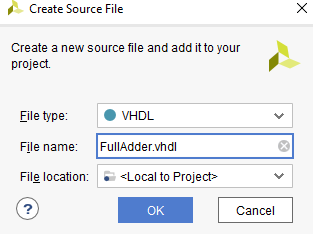

- Введите имя файла FullAdder.vhdl и нажмите ОК . :

Рисунок 4.13. Диалог создания исходного файла

- Повторите два предыдущих шага, чтобы создать еще один файл с именем Adder4.vhdl, затем нажмите Готово . в Добавить или создать источники дизайна диалог.

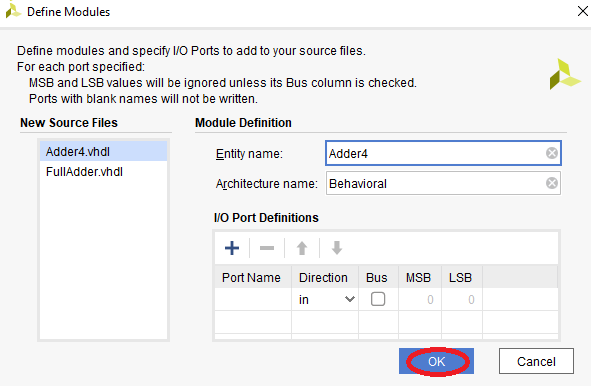

- Определить модули появится диалоговое окно. Здесь мы ничего вводить не будем. Нажмите ОК . чтобы закрыть это. Вас спросят, уверены ли вы, что хотите использовать эти значения. Нажмите Да . :

Рисунок 4.14. Диалог определения модулей

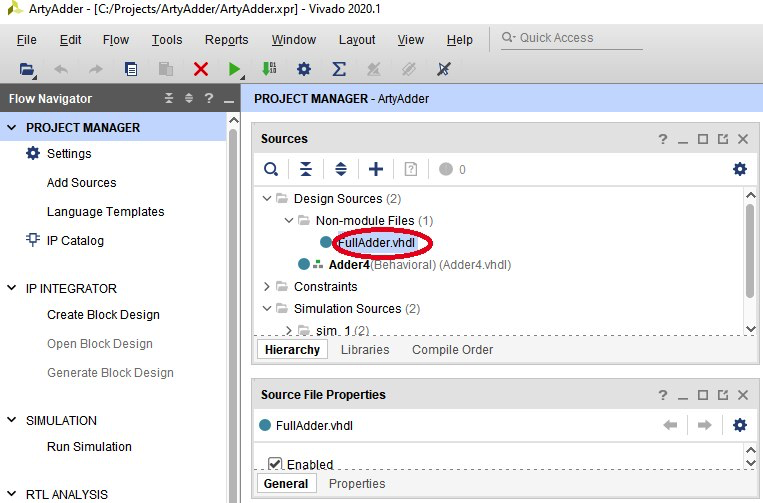

- Разверните Немодульные файлы . в разделе Источники дизайна , затем дважды щелкните FullAdder.vhdl. Откроется окно редактора с пустым файлом FullAdder.vhdl:

Рисунок 4.15. Недавно созданный исходный файл

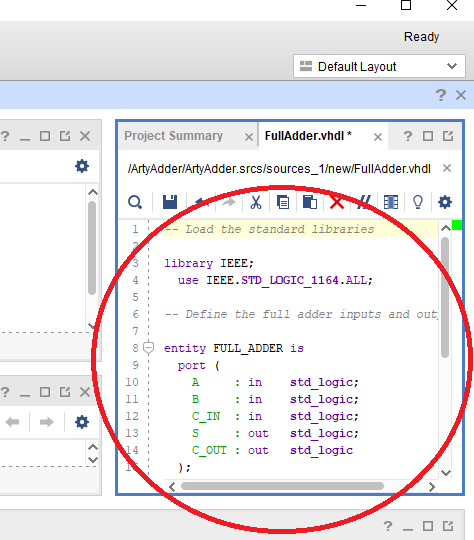

- Введите следующий код VHDL в окно редактора FullAdder.vhdl:

- Загрузить стандартные библиотеки библиотеки IEEE; use IEEE.STD_LOGIC_1164.ALL; - Определить полные входы и выходы сумматора. FULL_ADDER - это порт (A:в std_logic; B:в std_logic; C_IN:в std_logic; S:из std_logic; C_OUT:из std_logic); конечный объект; FULL_ADDER; - Определить поведение полной аддерархитектуры BEHAVIORAL FULL_ADDER isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A AND B) OR ((A XOR B) AND C_IN); конечная архитектура BEHAVIORAL;

Это тот же однобитовый полный код сумматора, который мы исследовали на языках проектирования оборудования . раздел главы 1, Архитектура высокопроизводительных встроенных систем . Рисунок 4.16 показывает код в окне редактора Vivado:

Рисунок 4.16 - Исходный код FullAdder.vhdl

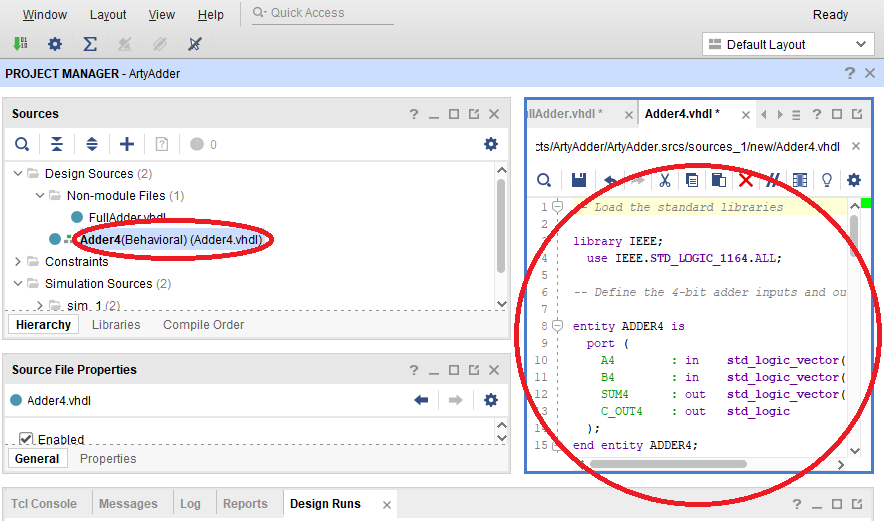

- Таким же образом дважды щелкните Adder4 (Behavioral) (Adder4.vhdl) . в разделе Источники дизайна . Удалите автоматически заполненное содержимое Adder4.vhdl . окно редактора и введите следующий код в Adder4.vhdl редактор:

- Загрузить стандартные библиотеки библиотеки IEEE; use IEEE.STD_LOGIC_1164.ALL; - Определите 4-битные входы и выходы сумматора. ADDER4 - это порт (A4:в std_logic_vector (3 вниз до 0); B4:в std_logic_vector (3 вниз до 0); SUM4:из std_logic_vector (3 вниз до 0) ); C_OUT4:out std_logic); end entity ADDER4; - Определение поведения 4-битной аддерархитектуры BEHAVIORAL ADDER4 is - Ссылка на предыдущее определение компонента полного сумматора FULL_ADDER is port (A:in std_logic; B:in std_logic; C_IN:в std_logic; S:выход std_logic; C_OUT:выход std_logic); конечный компонент; - Определите сигналы, используемые внутри 4-битного сумматора сигнала c0, c1, c2:std_logic; begin - Вход переноса в первый сумматор установлен на 0 FULL_ADDER0:FULL_ADDER карта портов (A => A4 (0), B => B4 (0), C_IN => '0', S => SUM4 (0), C_OUT => c0); FULL_ADDER1:карта портов FULL_ADDER (A => A4 (1), B => B4 (1), C_IN => c0, S => SUM4 (1), C_OUT => c1); FULL_ADDER2:карта портов FULL_ADDER (A => A4 (2), B => B4 (2), C_IN => c1, S => SUM4 (2), C_OUT => c2); FULL_ADDER3:карта портов FULL_ADDER (A => A4 (3), B => B4 (3), C_IN => c2, S => SUM4 (3), C_OUT => C_OUT4); конец архитектуры ПОВЕДЕНЧЕСКИЙ;

Этот код создает четыре копии однобитового полного сумматора. Перенос в наименее значимый сумматор устанавливается равным нулю, и перенос от каждого сумматора колеблется в следующий старший сумматор. Результатом сложения двух 4-битных чисел является 4-битный результат и однобитовый перенос:

Рисунок 4.17. Исходный код Adder4.vhdl

В следующей статье будет показано, как протестировать дизайн и реализовать наш дизайн для платы Arty.

Перепечатано с разрешения Packt Publishing. Авторские права © 2021 Packt Publishing

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT).

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT). Связанное содержание:

- Встроенный дизайн с ПЛИС:аппаратные ресурсы

- Встроенный дизайн с ПЛИС:языки реализации

- Встроенный дизайн с ПЛИС:процесс разработки

- Инструменты с открытым исходным кодом помогают упростить программирование FPGA.

- Реализация алгоритмов с плавающей запятой в ПЛИС или ASIC.

- Использование ПЛИС для глубокого обучения

- Программные инструменты переносят код GPU на FPGA для приложений AI.

- ПЛИС вытесняют ASIC в системе ADAS на базе зрения Subaru Eyesight.

Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Жидкостное аддитивное производство:построение 3D-объектов с жидкостью

- Что такое дизайн встроенной системы:этапы процесса проектирования

- Превращение больших данных в интеллектуальные данные с помощью встроенного ИИ

- Arrow Electronics запускает европейский конкурс разработчиков FPGA

- Конструкторский комплект для измерения артериального давления с помощью оптического датчика

- Дебют ПЛИС оборонного уровня с ранним доступом

- Создание роботов с Raspberry Pi и Python

- Создание сегвея с Raspberry Pi

- GoPiGo v2 с Windows IoT

- Все вместе с добавками