Начало работы с языком описания оборудования Verilog

В этой статье мы изучим базовую структуру модуля Verilog, рассмотрим некоторые примеры использования типа данных Verilog «провод» и его векторной формы и кратко коснемся некоторых различий между VHDL и Verilog.

В этой статье мы изучим базовую структуру модуля Verilog, рассмотрим несколько примеров использования «проводного» типа данных Verilog и его векторной формы, а также кратко коснемся некоторых различий между VHDL и Verilog.

Verilog и VHDL - два языка, которые обычно используются для описания цифровых схем. У AAC есть серия технических статей, в которых обсуждаются основные концепции VHDL. Эта статья является отправной точкой для нашей серии статей о Verilog.

Нужны ли мне и Verilog, и VHDL?

Прежде чем начать обсуждение, давайте обратимся к очевидному вопросу:действительно ли нам нужно знать оба этих языка?

И Verilog, и VHDL - мощные инструменты, которые можно использовать для разработки сложных цифровых схем. Хотя между этими двумя HDL есть некоторые различия, вы можете выбрать любой из них для освоения и использования. Однако я считаю, что в какой-то момент вам будет полезно иметь хотя бы базовое понимание обоих языков. Иногда, как дизайнерам, нам нужен фрагмент кода, чтобы получить представление о кодировании проекта. Мы сидим в сети часами и наконец находим то, что нам нужно, но для нас это не имеет смысла - это написано на языке HDL, который нам совершенно незнаком. Без базового понимания языка мы не сможем полностью понять методы.

Verilog Evolution

Verilog был разработан в начале 1984 года компанией Gateway Design Automation (примерно через три года после того, как VHDL был инициирован Министерством обороны США). Благодаря поддержке Министерства обороны, VHDL стал стандартом IEEE в 1987 году. Verilog не появлялся на сцене до 1995 года. Сегодня и VHDL, и Verilog являются популярными HDL, а инструменты проектирования FPGA обычно поддерживают оба языка.

Слово «Verilog» - это комбинация слов «проверка» и «логика», потому что этот язык впервые был предложен как инструмент моделирования и проверки. Давайте начнем с концепций и синтаксиса Verilog.

Пример 1

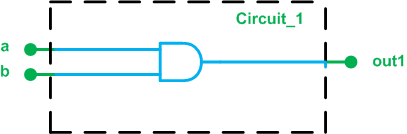

В качестве первого примера напишем код Verilog для схемы, изображенной на рисунке 1.

Рисунок 1. Схема_1

Есть два входа и один выход. Все порты имеют ширину в один бит. Функциональность схемы заключается в соединении логического И двух входов и передаче результата на порт out1.

Одно из возможных описаний Verilog для модуля Circuit_1:

Строки 1 и 8

В этих двух строках используются ключевые слова «module» и «endmodule», чтобы указать, что все строки между ними (строки 2–7) описывают цепь с именем «Circuit_1». Это имя произвольно и позволяет нам ссылаться на эту схему позже.

Строки 2–6

Эти строки определяют интерфейс «Circuit_1» с окружающей средой. Порты ввода и вывода описываются ключевыми словами «input» и «output». За этими ключевыми словами следует другое ключевое слово «провод», а затем имя порта (см. Рисунок 1). Что указывает ключевое слово «провод»? «Wire» - это тип данных Verilog, представляющий физический провод в проекте. Мы обсудим типы данных Verilog более подробно в следующей статье, но пока мы знаем, что в нашем модуле будет три провода с именами a, b и out1, и, поскольку они указаны в объявлении порта, они соответствуют интерфейс модуля.

Строка 7

В этой строке используется побитовый оператор AND, то есть &, для описания функциональности схемы. Ключевое слово assign помещает a &b в выходной порт out1. Этот тип назначения называется непрерывным назначением. Он называется так, потому что присвоение всегда активно, когда изменяется операнд в правой части, a &b вычисляется и присваивается out1. Мы можем представить себе непрерывное назначение как комбинационную схему, выход которой постоянно обновляется в зависимости от входов. В нашем примере комбинационная схема представляет собой простой логический элемент И. В Verilog HDL также есть процедурные назначения, которые будут обсуждаться в следующих статьях.

Теперь мы можем использовать программный пакет, такой как Xilinx ISE, для проверки приведенного выше кода. Вы можете найти руководство по этому программному обеспечению на основе Verilog здесь (PDF).

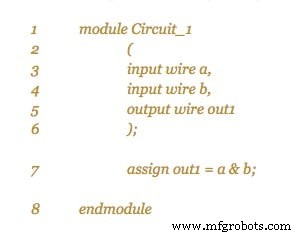

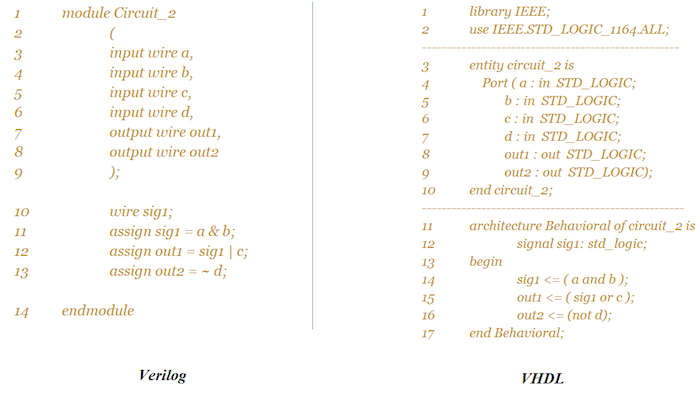

Сравнение примера 1 с кодом VHDL

На рисунке 2 ниже показаны описания Verilog и VHDL для модуля Circuit_1.

Рисунок 2. Сравнение описаний Verilog и VHDL для Circuit_1.

Как видите, нам нужно включить некоторые библиотеки при кодировании на VHDL. Эти библиотеки дают определение типов данных и операторов. Учитывая добавление этих библиотек и общий формат VHDL, мы заметили, что код VHDL более подробный. Однако такая многословность не лишена преимуществ. Например, функция управления библиотеками VHDL может быть полезна при моделировании систем более высокого уровня. В будущих статьях мы время от времени будем обсуждать плюсы и минусы этих двух HDL.

Verilog имеет четырехзначную систему

В большинстве типов данных Verilog используются четыре основных значения. Провода, определенные в листинге 1, могут принимать одно из следующих значений:

- 0:для низкого логического уровня или ложного состояния.

- 1:для высокого или истинного логического состояния.

- z:для состояния с высоким импедансом (может использоваться для описания вывода буфера с тремя состояниями)

- x:для безразличного или неизвестного значения (когда вход не инициализирован или два или более конфликтующих выхода соединены вместе).

Тип данных VHDL std_logic может принимать девять различных значений, но обычно используются значения «0», «1», «Z» и «-» («-» означает «безразлично»).

Пример 2

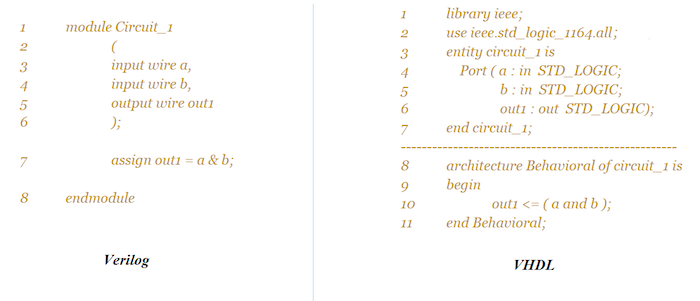

В качестве другого примера давайте напишем код Verilog для схемы (которую мы обозначим как Circuit_2), показанной на рисунке 3.

Рисунок 3. Схема_2

Следующий код Verilog описывает эту схему:

Элементы, используемые в приведенном выше коде, аналогичны элементам в примере 1, за исключением того, что внутренний сигнал определен в строке 10 кода. Ключевое слово «провод» используется для указания типа данных этого соединения. Как обсуждалось выше, тип данных «провод» будет преобразован в физический провод в проекте.

В приведенном выше коде также используются некоторые новые побитовые операторы Verilog:~ для НЕ и | для операции ИЛИ. Еще один полезный побитовый оператор ^ для операции XOR. На рисунке 4 показаны описания Verilog и VHDL для модуля Circuit_2. Такие сравнения могут помочь вам увидеть различия и сходства между этими двумя языками.

Рисунок 4. Сравнение описаний Verilog и VHDL для Circuit_2.

Пример 3

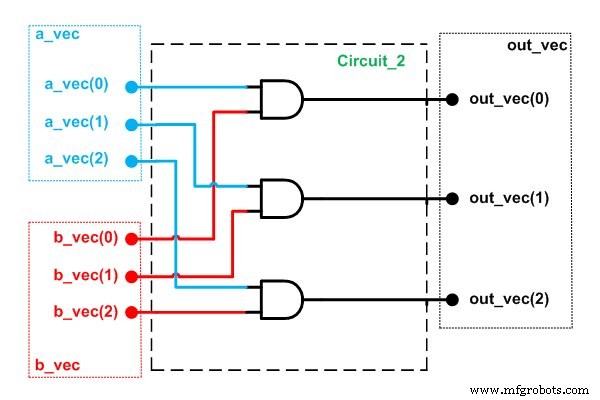

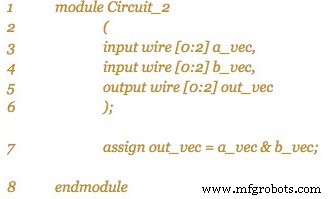

Для нашего третьего и последнего примера мы дадим код Verilog для схемы, показанной на рисунке 5.

Рисунок 5. Схема для примера 3.

Как видите, между синими входными портами и красными существует определенная взаимосвязь:соответствующие входы объединяются оператором AND. Результат присваивается выходному порту. В таких случаях мы можем сгруппировать сигналы и рассматривать их как вектор. Это делает код компактным и читаемым.

Используя концепцию вектора в Verilog, мы можем легко расширить код в листинге 1, чтобы описать приведенную выше схему (см. Код в листинге 3 ниже).

Обратите внимание, что диапазон индексов векторов может быть либо возрастающим ([0:2], как использовалось выше), либо убыванием ([2:0]). Хотя выше используется восходящий формат, обычно он менее подвержен ошибкам при использовании нисходящей формы. Это связано с тем, что нисходящий стиль соответствует нашему восприятию, что крайняя левая позиция двоичного числа имеет наивысший индекс. Обратите внимание, что векторы также используются в VHDL.

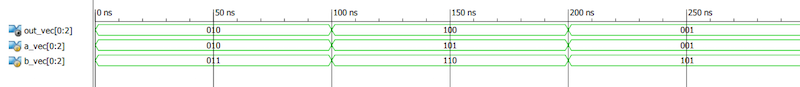

На рисунке 6 ниже показана ISE-симуляция кода из листинга 3.

Рисунок 6. ISE-симуляция кода примера 3 .

В этой статье мы обсудили, что изучать и VHDL, и Verilog - хорошая идея, мы изучили базовую структуру модуля Verilog и познакомились с «проводным» типом данных Verilog и его векторной формой. Мы также кратко коснулись некоторых различий между VHDL и Verilog. В следующей статье нашей серии о Verilog будет обсуждаться разработка комбинационных схем в Verilog.

Встроенный

- Готовые контейнеры для кода:начало работы с инструментами автоматизации процессов в облаке

- Начало работы с керамической 3D-печатью

- Начало работы с TJBot

- Начало работы с RAK 831 Lora Gateway и RPi3

- Начало работы со шлюзом RAK831 LoRa и RPi3

- Как начать работу с выводом ИИ на периферии

- Начало работы с Eagle Group:что вам нужно знать

- Начало работы с My.Cat.com

- Node-RED и начало работы с Docker

- Начало работы с Go on PLCnext