Дельта-сигма АЦП

Одна из наиболее продвинутых технологий АЦП - это так называемая дельта-сигма, или ΔΣ (с использованием правильной записи греческих букв). В математике и физике заглавная греческая буква дельта (Δ) обозначает разницу . или изменить , а заглавная буква сигма (Σ) представляет суммирование :сложение нескольких терминов вместе. Иногда этот преобразователь обозначается теми же греческими буквами в обратном порядке:сигма-дельта или ΣΔ.

В преобразователе ΔΣ аналоговый входной сигнал напряжения подключается к входу интегратора, создавая скорость изменения или крутизну напряжения на выходе, соответствующую входной величине. Затем это нарастающее напряжение сравнивается с потенциалом земли (0 В) с помощью компаратора.

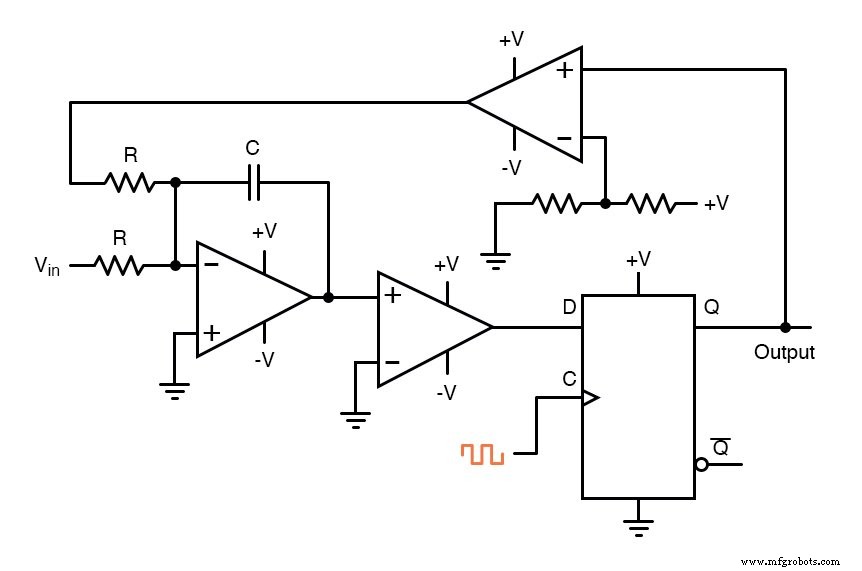

Компаратор действует как своего рода 1-битный АЦП, вырабатывая 1 бит на выходе («высокий» или «низкий») в зависимости от того, является ли выход интегратора положительным или отрицательным. Затем выход компаратора фиксируется через триггер D-типа, синхронизируемый с высокой частотой, и возвращается . к другому входному каналу интегратора, чтобы управлять интегратором в направлении выхода 0 В. Базовая схема выглядит так:

Принципиальная схема

Крайний левый операционный усилитель является интегратором (суммирующим). Следующий операционный усилитель, на который подается интегратор, - это компаратор или 1-битный АЦП. Затем идет триггер D-типа, который фиксирует выход компаратора при каждом тактовом импульсе, отправляя сигнал «высокий» или «низкий» следующему компаратору в верхней части схемы.

Этот последний компаратор необходим для преобразования однополярного выходного напряжения логического уровня 0 В / 5 В триггера в сигнал напряжения + V / -V, который будет возвращен интегратору. Если выход интегратора положительный, первый компаратор выдает «высокий» сигнал на вход D триггера.

При следующем тактовом импульсе этот «высокий» сигнал будет выведен из линии Q на неинвертирующий вход последнего компаратора. Этот последний компаратор, видя, что входное напряжение превышает пороговое напряжение 1/2 + V, насыщается в положительном направлении, посылая полный сигнал + V на другой вход интегратора.

Этот сигнал обратной связи + V имеет тенденцию управлять выходным сигналом интегратора в отрицательном направлении. Если это выходное напряжение когда-либо станет отрицательным, контур обратной связи отправит корректирующий сигнал (-V) обратно на верхний вход интегратора, чтобы направить его в положительном направлении.

Это принцип дельта-сигма в действии:первый компаратор обнаруживает разницу (Δ) между выходом интегратора и нулевым напряжением. Интегратор суммирует (Σ) выход компаратора с аналоговым входным сигналом.

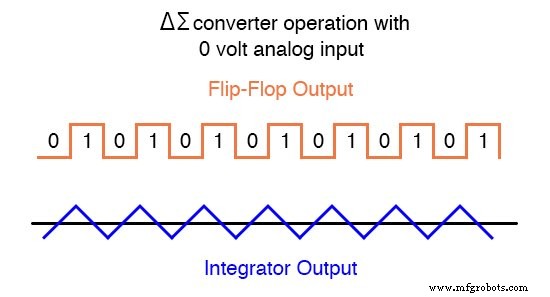

Функционально это приводит к последовательному потоку битов, выводимых триггером. Если аналоговый вход равен нулю вольт, интегратор не будет иметь тенденции к линейному увеличению ни положительного, ни отрицательного, кроме как в ответ на напряжение обратной связи.

В этом сценарии выходной сигнал триггера будет постоянно колебаться между «высоким» и «низким», поскольку система обратной связи «рыскает» вперед и назад, пытаясь поддерживать выход интегратора на уровне нуля вольт:

Формы выходных сигналов

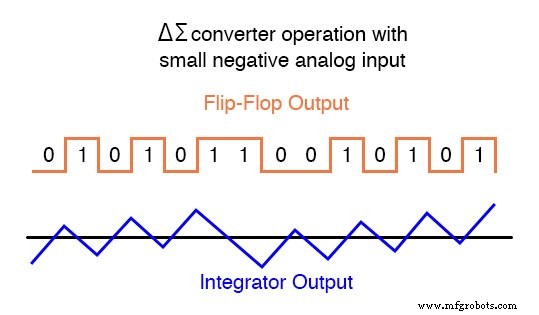

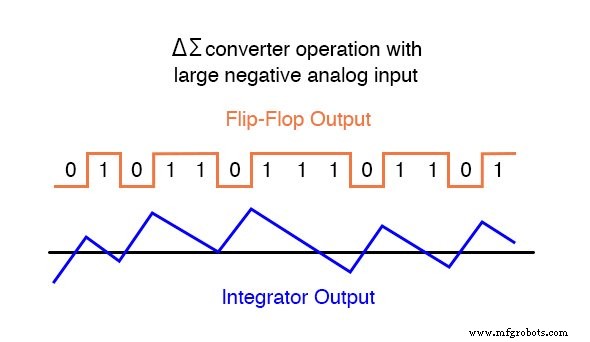

Если, однако, мы подадим отрицательное аналоговое входное напряжение, интегратор будет иметь тенденцию изменять свой выходной сигнал в положительном направлении. Обратная связь может только добавить к линейному изменению интегратора фиксированным напряжением в течение фиксированного времени, поэтому выходной поток битов триггером будет не таким же:

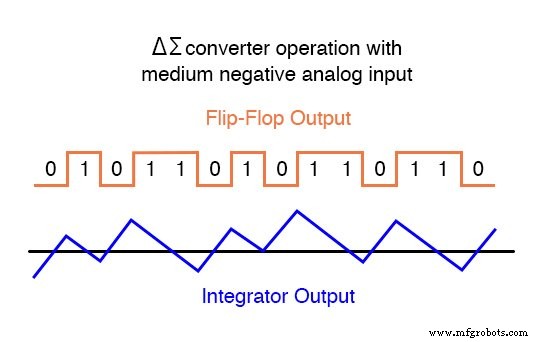

Подавая больший (отрицательный) аналоговый входной сигнал на интегратор, мы заставляем его выход более круто нарастать в положительном направлении. Таким образом, система обратной связи должна выдать больше единиц, чем раньше, чтобы вернуть выход интегратора к нулю вольт:

По мере увеличения величины аналогового входного сигнала увеличивается и появление единиц на цифровом выходе триггера:

Параллельный выход двоичного числа получается из этой схемы путем усреднения последовательного потока битов вместе. Например, схема счетчика может быть разработана для сбора общего количества единиц, выдаваемых триггером за заданное количество тактовых импульсов. Это число будет показывать аналоговое входное напряжение.

Существуют вариации на эту тему с использованием нескольких каскадов интегратора и / или схем компаратора, выводящих более 1 бита, но одна концепция, общая для всех преобразователей ΔΣ, - это концепция передискретизации . Передискретизация - это когда несколько выборок аналогового сигнала берутся АЦП (в данном случае 1-битным АЦП), и эти оцифрованные выборки усредняются.

Конечным результатом является эффективное увеличение количества битов, выделяемых из сигнала. Другими словами, 1-битный АЦП с избыточной дискретизацией может выполнять ту же работу, что и 8-битный АЦП с однократной дискретизацией, хотя и с меньшей частотой.

СВЯЗАННЫЙ РАБОЧИЙ ЛИСТ:

- Таблица аналого-цифрового преобразования

Промышленные технологии