Асинхронные счетчики

В предыдущем разделе мы видели схему, в которой используется один триггер JK, который ведет обратный отсчет в двухбитовой двоичной последовательности от 11 до 10 до 01 до 00.

Поскольку было бы желательно иметь схему, которая могла бы считать вперед и не только в обратном направлении, было бы целесообразно еще раз изучить последовательность прямого счета и найти больше шаблонов, которые могли бы указать, как построить такую схему.

Поскольку мы знаем, что двоичные счетные последовательности следуют схеме деления частоты на октаву (коэффициент 2) и что мультивибраторы JK-триггера, настроенные для режима «переключения», способны выполнять этот тип частотного деления, мы можем представить себе схему состоит из нескольких триггеров JK, соединенных каскадом для получения четырех битов вывода.

Основная проблема, с которой мы сталкиваемся, - это определить, как соединить эти триггеры вместе так, чтобы они переключались в нужное время для создания правильной двоичной последовательности.

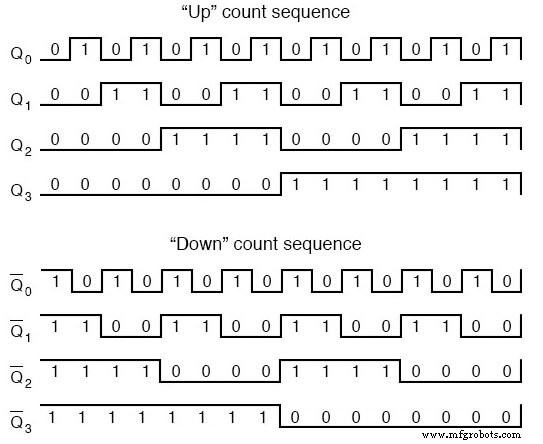

Изучите следующую последовательность двоичного счета, обращая внимание на шаблоны, предшествующие «переключению» бита между 0 и 1:

Обратите внимание, что каждый бит в этой четырехбитовой последовательности переключается, когда бит перед ним (бит, имеющий меньшее значение или весовой коэффициент) переключается в определенном направлении:от 1 до 0.

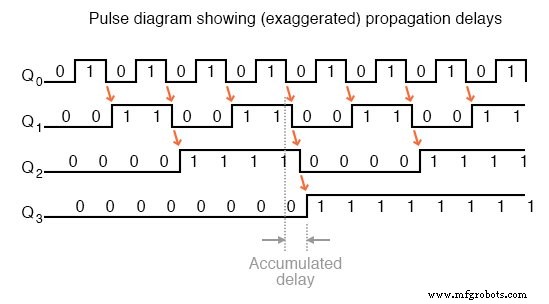

Маленькие стрелки указывают те точки в последовательности, в которых бит переключается, причем острие стрелки указывает на переход предыдущего бита из состояния «высокий» (1) в состояние «низкий» (0):

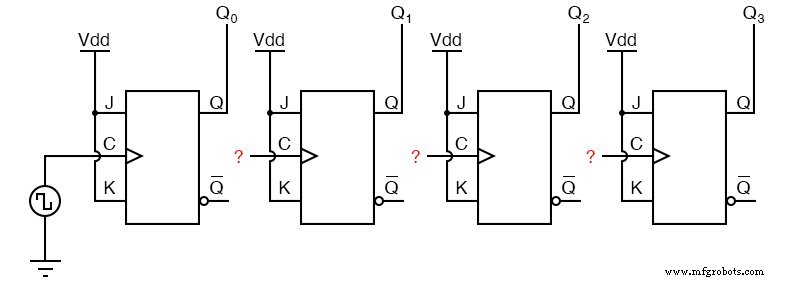

Начиная с четырех триггеров JK, подключенных таким образом, чтобы всегда находиться в режиме «переключения», нам нужно определить, как подключить входы синхронизации таким образом, чтобы каждый последующий бит переключался, когда бит перед ним переходит из 1 до 0.

Выходы Q каждого триггера будут служить соответствующими двоичными битами окончательного четырехбитного счетчика:

Если бы мы использовали триггеры с запуском по отрицательному фронту (пузырьковые символы на тактовых входах), мы могли бы просто подключить тактовый вход каждого триггера к выходу Q триггера перед ним, так что когда бит перед ним он изменяется с 1 на 0, «спадающий фронт» этого сигнала будет «синхронизировать» следующий триггер, чтобы переключить следующий бит:

Четырехбитный счетчик «вверх»

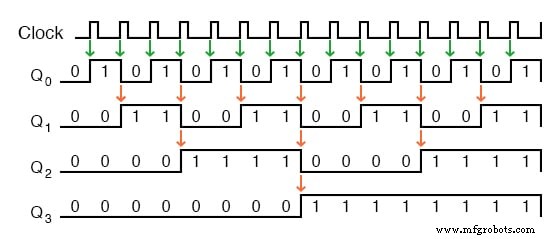

Эта схема будет выдавать следующие формы выходных сигналов, когда "синхронизируется" повторяющимся источником импульсов от генератора:

Первый триггер (с Q 0 output), имеет тактовый вход, запускаемый по положительному фронту, поэтому он переключается с каждым нарастающим фронтом тактового сигнала.

Обратите внимание, как тактовый сигнал в этом примере имеет рабочий цикл менее 50%.

Я показал сигнал таким образом, чтобы продемонстрировать, что тактовый сигнал не обязательно должен быть симметричным для получения надежных, «чистых» выходных битов в нашей четырехбитовой двоичной последовательности.

В самой первой схеме триггера, показанной в этой главе, я использовал сам тактовый сигнал как один из выходных битов.

Однако это плохая практика в конструкции счетчика, поскольку она требует использования прямоугольного сигнала с рабочим циклом 50% («высокое» время =«низкое» время), чтобы получить последовательность подсчета, в которой каждый шаг делает паузу на такое же время.

Однако использование одного триггера JK для каждого выходного бита избавляет нас от необходимости иметь симметричный тактовый сигнал, позволяя использовать практически любое разнообразие сигналов высокого / низкого уровня для увеличения последовательности счета.

Как указано всеми другими стрелками на диаграмме импульсов, каждый последующий выходной бит переключается действием предыдущего бита, переходящего от «высокого» (1) к «низкому» (0).

Это шаблон, необходимый для создания последовательности счета «вверх».

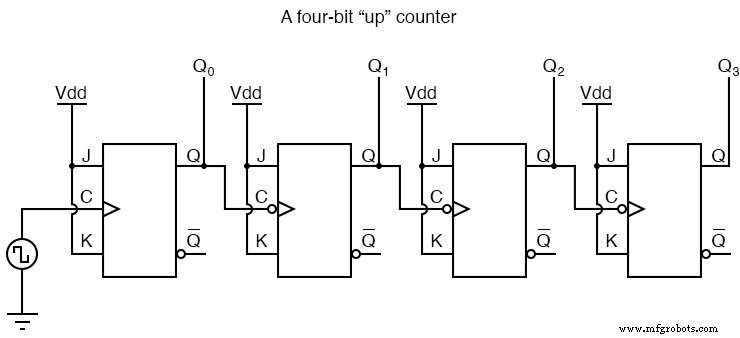

Менее очевидное решение для генерации «восходящей» последовательности с использованием триггеров, запускаемых по положительному фронту, - это «синхронизировать» каждый триггер, используя выход Q ’предыдущего триггера, а не выход Q.

Поскольку выход Q 'всегда будет полностью противоположным состоянием выхода Q на триггере JK (недопустимые состояния с этим типом триггера), переход от высокого к низкому на выходе Q будет сопровождаться переход от низкого к высокому на выходе Q '.

Другими словами, каждый раз, когда выход Q триггера переходит с 1 на 0, выход Q 'того же триггера будет переходить с 0 на 1, обеспечивая положительный тактовый импульс, который нам понадобится для переключения триггер, срабатывающий по положительному фронту, в нужный момент:

Альтернативный четырехбитный счетчик «вверх»

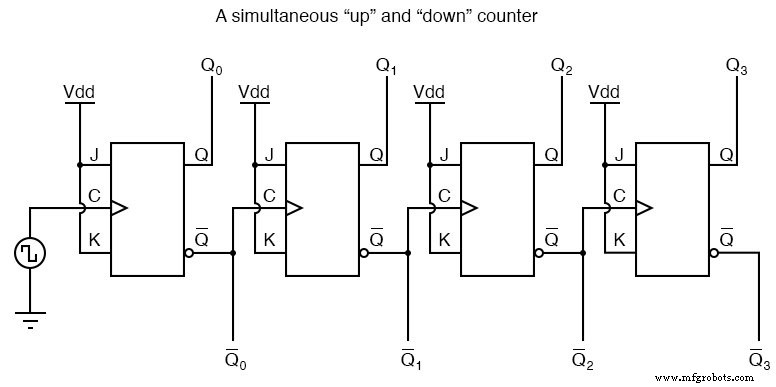

Один из способов расширить возможности любой из этих двух схем счетчика - это рассматривать выходы Q ’как еще один набор из четырех двоичных разрядов.

Если мы рассмотрим диаграмму импульсов для такой схемы, мы увидим, что выходы Q ’генерируют понижение -счетная последовательность, в то время как выходы Q генерируют вверх -счетная последовательность:

Одновременный счетчик «вверх» и «вниз»

К сожалению, все схемы счетчиков, показанные до сих пор, имеют общую проблему: пульсация эффект.

Этот эффект наблюдается в некоторых типах двоичных сумматоров и схем преобразования данных и связан с накопительными задержками распространения между каскадными вентилями.

Когда выход Q триггера переходит с 1 в 0, он дает команду на переключение следующему триггеру.

Если следующее переключение триггера представляет собой переход от 1 к 0, он также подает команду на переключение триггера после него и так далее.

Однако, поскольку всегда существует небольшая задержка распространения между командой переключения (тактовый импульс) и фактической реакцией переключения (выходы Q и Q 'меняют состояния), любые последующие переключаемые триггеры будут переключаться некоторое время после переключился первый триггер.

Таким образом, когда несколько битов переключаются в последовательности двоичного счета, они не все переключаются в одно и то же время:

Недостаток схемы асинхронного счетчика:задержка распространения

Как видите, чем больше битов переключается с данным тактовым импульсом, тем серьезнее накопленное время задержки от LSB к MSB.

Когда тактовый импульс возникает в такой точке перехода (скажем, при переходе от 0111 к 1000), выходные биты будут «колебаться» в последовательности от LSB к MSB, поскольку каждый последующий бит переключается и также дает команду на переключение следующего бита. , с небольшой задержкой распространения между каждым переключением битов.

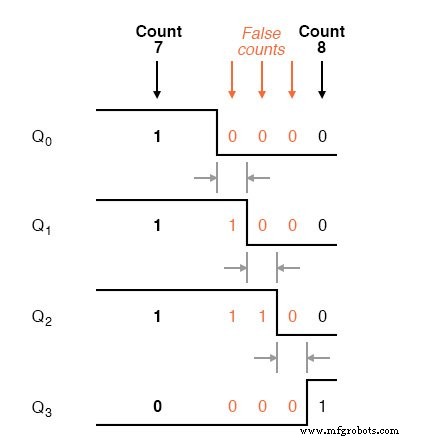

Если мы внимательно посмотрим на этот эффект во время перехода от 0111 к 1000, мы увидим, что будет false количество выходных данных, сгенерированное за короткий период времени, когда имеет место эффект «пульсации»:

Вместо простого перехода с выхода «0111» на выход «1000», схема счетчика будет очень быстро колебаться от 0111 до 0110, от 0100 до 0000 до 1000 или от 7 до 6 до 4 до 0 а затем до 8. Такое поведение дает схеме счетчика имя счетчик пульсаций . , или асинхронный счетчик .

Схема счетчика стробоскопических сигналов

Во многих приложениях этот эффект допустим, поскольку пульсация происходит очень и очень быстро (ширина задержек здесь преувеличена, чтобы помочь понять эффекты).

Если бы все, что мы хотели сделать, это подключить набор светодиодов (LED) к выходам счетчика, например, эта короткая пульсация не имела бы никакого значения.

Однако, если бы мы хотели использовать этот счетчик для управления входами «выбора» мультиплексора, индексирования указателя памяти в схеме микропроцессора (компьютера) или выполнения какой-либо другой задачи, где ложные выходы могут вызвать ложные ошибки, это было бы неприемлемо. .

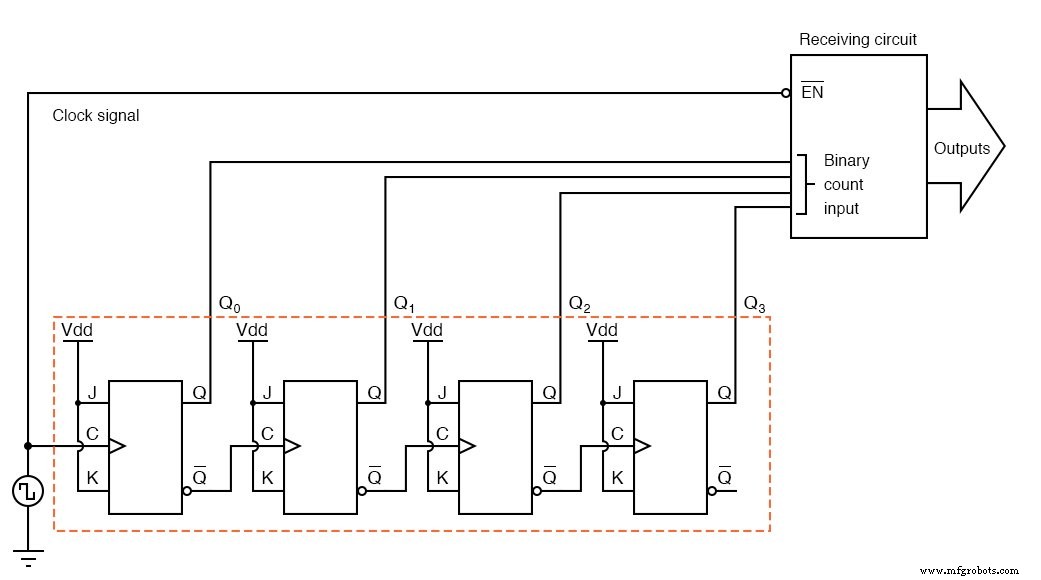

Есть способ использовать этот тип схемы счетчика в приложениях, чувствительных к ложным выводам, генерируемым пульсациями, и он включает принцип, известный как стробирование .

Большинство схем декодеров и мультиплексоров оснащены по крайней мере одним входом, который называется «разрешить».

Выходы такой схемы будут активны только тогда, когда активен вход разрешения.

Мы можем использовать этот вход включения для стробоскопа схема, принимающая выходной сигнал счетчика пульсаций, так что он отключен (и, таким образом, не отвечает на выход счетчика) в течение короткого периода времени, в течение которого выходы счетчика могут колебаться, и включается только тогда, когда прошло достаточно времени с момента последнего тактового импульса что вся рябь прекратится.

В большинстве случаев стробирующий сигнал может быть тем же синхроимпульсом, который управляет схемой счетчика:

При активном низком входном разрешении принимающая схема будет реагировать на двоичный счет схемы четырехбитного счетчика только тогда, когда тактовый сигнал имеет низкий уровень.

Как только тактовый импульс становится «высоким», приемная схема перестает реагировать на выходной сигнал счетной схемы.

Поскольку схема счетчика запускается по положительному фронту (как определено первым вход триггера), все действия подсчета происходят при переходе синхросигнала с низкого на высокий, что означает, что приемная схема будет отключена непосредственно перед тем, как произойдет какое-либо переключение на четырех выходных битах схемы счетчика.

Приемная цепь не будет включена до тех пор, пока тактовый сигнал не вернется в низкое состояние, что должно быть достаточно долгое время после вся рябь перестала быть «безопасной», чтобы новый счетчик мог повлиять на приемную цепь.

Ключевым параметром здесь является «высокое» время тактового сигнала:оно должно быть не меньше максимального ожидаемого периода пульсации схемы счетчика.

В противном случае синхронизирующий сигнал преждевременно включит приемную цепь, в то время как некоторая пульсация все еще имеет место.

Недостаток схемы асинхронного счетчика:ограниченная скорость

Еще один недостаток асинхронной схемы счетчика пульсаций - это ограниченная скорость.

Хотя все схемы затворов ограничены с точки зрения максимальной частоты сигнала, конструкция схем асинхронных счетчиков усугубляет эту проблему, делая задержки распространения аддитивными.

Таким образом, даже если в приемной цепи используется стробирование, схема асинхронного счетчика не может синхронизироваться ни с какой частотой выше, чем та, которая позволяет максимально возможной накопленной задержке распространения пройти задолго до следующего импульса.

Решением этой проблемы является схема счетчика, полностью исключающая пульсации.

Такая схема счетчика избавит от необходимости разрабатывать функцию «стробирования» в любых цифровых схемах, использующих выход счетчика в качестве входа, а также будет иметь гораздо большую рабочую скорость, чем его асинхронный эквивалент.

Эта конструкция схемы счетчика является предметом следующего раздела.

ОБЗОР:

- Счетчик «вверх» может быть получен путем подключения тактовых входов JK-триггеров, запускаемых по положительному фронту, к выходам Q ’предыдущих триггеров. Другой способ - использовать триггеры, запускаемые по отрицательному фронту, соединив тактовые входы с выходами Q предыдущих триггеров. В любом случае входы J и K всех триггеров подключены к V cc или V dd чтобы всегда быть «под кайфом».

- Счетные схемы, состоящие из каскадных триггеров JK, где каждый тактовый вход получает свои импульсы с выхода предыдущего триггера, неизменно демонстрирует эффект пульсации , где ложные выходные счетчики генерируются между некоторыми шагами счетной последовательности. Эти типы счетных схем называются асинхронными счетчиками . или счетчики пульсации .

- Стробинг - это метод, применяемый к схемам, принимающим выходной сигнал асинхронного (пульсирующего) счетчика, так что ложные подсчеты, генерируемые во время пульсации, не будут иметь вредного воздействия. По сути, включить вход такой схемы подключен к тактовому импульсу счетчика таким образом, что он активируется только тогда, когда выходы счетчика не изменяются, и будет отключен в те периоды изменения выходов счетчика, где возникают пульсации.

СВЯЗАННЫЕ РАБОЧИЕ ТАБЛИЦЫ:

- Рабочий лист счетчика пульсаций

Промышленные технологии