Встроенный дизайн с FPGA:реализация

Наличие более мощных FPGA и более эффективных сред программирования сделало реализацию FPGA широко доступны, но использование ПЛИС может показаться сложной задачей.

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

1:аппаратные ресурсы

2:языки реализации

3:Процесс разработки

4:создание проекта

5. Реализация (эта статья)

Адаптировано из книги Джима Ледина "Архитектура высокопроизводительных встраиваемых систем".

Проверка логического поведения

Важно протестировать поведение логики с помощью моделирования, прежде чем пытаться запустить ее в ПЛИС. Это связано с тем, что в среде моделирования намного проще обнаружить и исправить проблемы, чем с логикой, работающей внутри FPGA. Инструменты моделирования Vivado очень хорошо отражают поведение схемы:

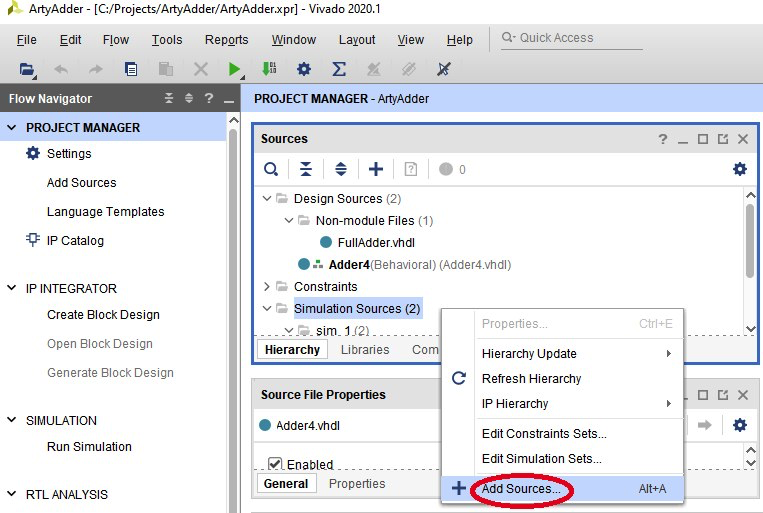

- В разделе Источники в дополнительном окне щелкните правой кнопкой мыши Источники моделирования и выберите Добавить источники… :

Рисунок 4.18 - Пункт меню «Добавить источники…» для источников моделирования

- В Добавить источники в диалоговом окне убедитесь, что Добавить или создать источники моделирования выбран, затем нажмите Далее .

- В Добавить или создать источники моделирования в диалоговом окне нажмите Создать файл . .

- Введите имя файла vhdl и нажмите ОК .

- Нажмите Готово . чтобы закрыть Добавить или создать источники моделирования диалоговое окно, затем нажмите ОК в Определить модуль диалоговое окно и нажмите Да когда вас спросят, уверены ли вы, что хотите использовать эти

- Дважды щелкните Adder4 TestBench (Behavioral) (Adder4TestBench.vhdl) . в разделе Источники моделирования . Удалите автоматически заполненное содержимое vhdl . окна редактора и введите следующий код в Adder4TestBench.vhdl редактор:

библиотека IEEE; используйте IEEE.STD_LOGIC_1164.ALL; используйте IEEE.NUMERIC_STD.ALL; объект ADDER4_TESTBENCH - это конечный объект ADDER4_TESTBENCH; архитектура BEHAVIORAL ADDER4_TESTBENCH - это компонент ADDER4 - это порт (A4:в std_logic_vector (3 downso 0); B4:in std_logic_vector (3 downso 0); B4:in std_logic_vector (3_download); 0); C_OUT4:out std_logic); конечный компонент; сигнал a:std_logic_vector (от 3 до 0); сигнал b:std_logic_vector (от 3 до 0); сигнал s:std_logic_vector (от 3 до 0); сигнал c_out:std_logic; сигнал ожидаемая_сумма5:без знака (с 4 до 0); сигнал ожидаемая_сумма4:без знака (от 3 до 0); сигнал ожидаемый_c:std_logic; ошибка сигнала:std_logic; начало TESTED_DEVICE:карта портов ADDER4 (A4 => a, B4 => b, SUM4 => s, C_OUT4 => c_out); ТЕСТ:начало процесса - Проверить все комбинации двух 4-битных слагаемых (всего 256 тестов) для a_val в цикле от 0 до 15 для b_val в цикле от 0 до 15 - Установить входы для компонента ADDER4 a <=std_logic_vector (to_unsigned ( a_val, a'length)); b <=std_logic_vector (to_unsigned (b_val, b'length)); ждать 1 нс; - Вычислить 5-битную сумму двух 4-битных значений expected_sum5 <=unsigned ('0' &a) + unsigned ('0' &b); ждать 1 нс; - Разбить сумму на 4-битный выход и бит переноса ожидаемая_сумма4 <=ожидаемая_сумма5 (от 3 до 0); ожидаемое_с <=ожидаемое_сумма5 (4); ждать 1 нс; - Сигнал 'error' перейдет в 1 только в случае возникновения ошибки, если ((unsigned (s) =unsigned (expected_sum4)) and (c_out =expected_c)) then error <='0'; иначе ошибка <='1'; конец, если; - Каждый проход по внутреннему циклу занимает 10 нс, ожидание 7 нс; конец петли; конец петли; ждать; КОНЕЧНЫЙ ТЕСТ процесса; конечная архитектура ПОВЕДЕНИЕ; Этот код реализует функции 4-битного сумматора, представляя все комбинации 4-битных чисел для каждого из A4 и B4 входные данные в Adder4 компонент. Он сравнивает SUM4 и C_OUT4 выходные данные Adder4 компонент для независимого вычисления значений для одних и тех же входных данных. После каждой операции добавления выдается ошибка signal установлено значение 0, если Adder4 выходы соответствуют ожидаемым значениям, либо задано значение 1 если есть несоответствие.

Код в Adder4TestBench.vhdl напоминает традиционный программный код тем, как он использует вложенные циклы for для применения всех тестовых входных комбинаций к Adder4 тестируемый компонент. Код, запускающий тесты в режиме моделирования, не является синтезируемым, что означает, что он не представляет собой чисто аппаратную логическую схему и может выполнять традиционные программные операции, такие как итеративное выполнение для петли.

Однако, как и в физических схемах, сигналы, которым присваиваются значения в коде испытательного стенда с использованием оператора <=, не могут использоваться в один и тот же момент времени в последующих выражениях. Это связано с тем, что среда моделирования представляет реальные эффекты задержки распространения, которая значительна даже в крошечных устройствах FPGA. Три ждут 1 нс ; Операторы в коде тестового стенда приостанавливают операции схемы, чтобы учесть задержку распространения. Эти задержки в 1 нс обеспечивают время для значений сигнала, вычисленных непосредственно перед wait оператор для распространения, чтобы их можно было использовать в следующем операторе. Последний ожидание 7 нс ; Оператор во внутреннем цикле представляет собой паузу, которая позволяет нам четко видеть результаты каждой итерации циклов моделирования на экране трассировки сигнала.

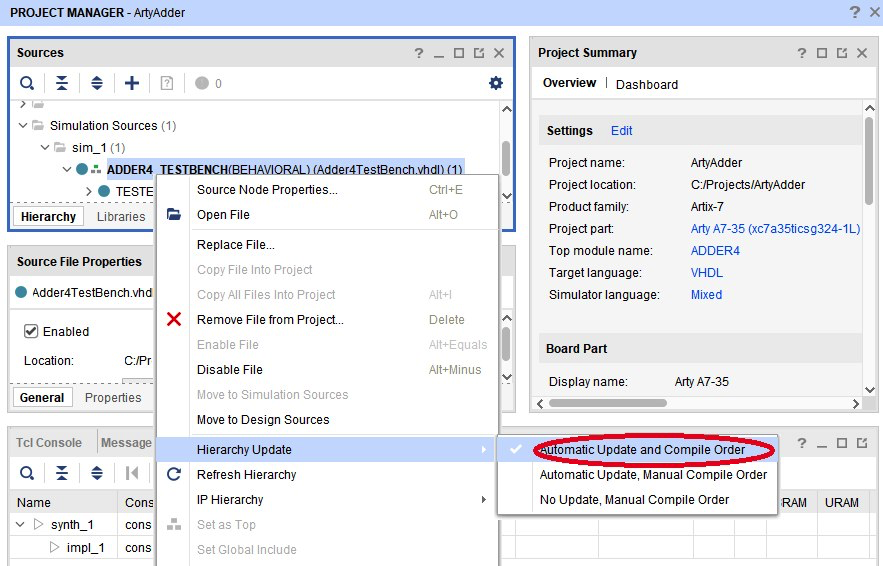

- Щелкните правой кнопкой мыши Adder4 TestBench (Behavioral) (Adder4TestBench.vhdl) . в разделе Источники моделирования и выберите Автоматическое обновление и порядок компиляции . . Это устанавливает ADDER4_TESTBENCH в качестве объекта верхнего уровня для запуска моделирования:

Рисунок 4.19. Выбор меню для установки автоматического обновления и порядка компиляции

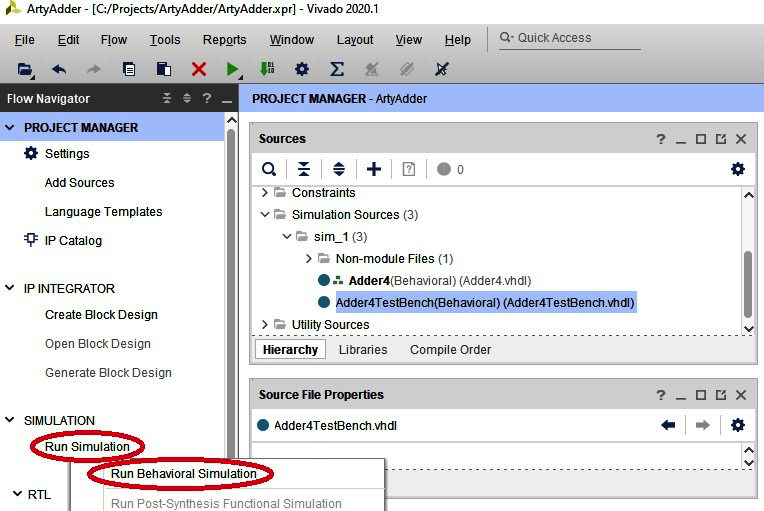

- Нажмите Запустить моделирование . , затем Запустить поведенческое моделирование в Навигаторе потока окно для входа в режим моделирования. Если вы еще не сохранили файлы редактора, вам будет предложено сделать это. Нажмите Сохранить . . Затем будет запущено моделирование:

Рисунок 4.20 - Выбор меню «Запустить поведенческое моделирование»

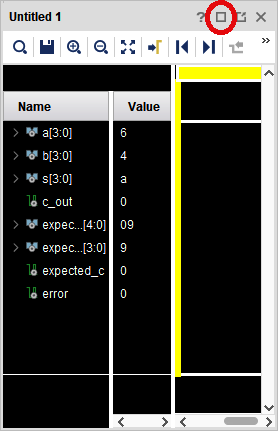

- Когда МОДЕЛИРОВАНИЕ В открывшемся окне нажмите кнопку развертывания в окне вывода моделирования с заголовком Без названия 1 :

Рисунок 4.21 - Окно результатов моделирования

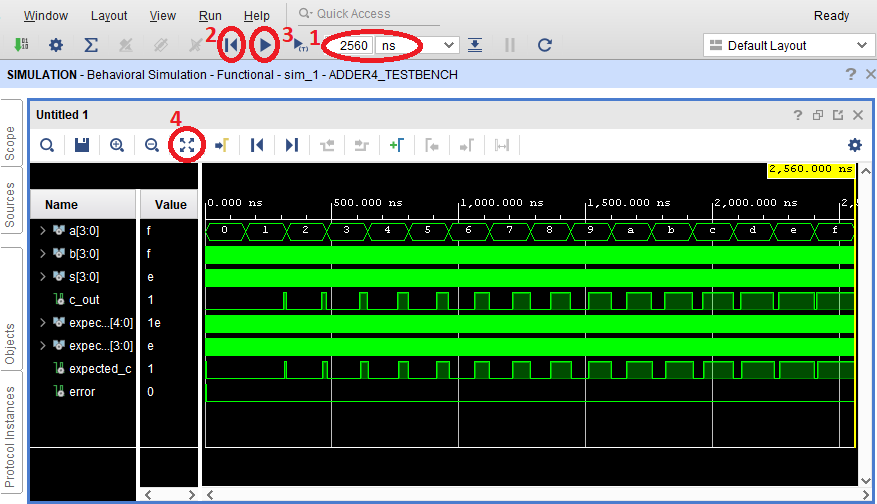

Общее время моделирования каждого прохождения внутреннего цикла составляет 10 нс. Поскольку цикл в Adder4TestBench.vhdl проходит 256 , время запуска моделирования - 2560 нс.

- Установите время выполнения моделирования на 2560 нс на верхней панели инструментов ( шаг 1 на следующем рисунке), нажмите кнопку перезапуска, указывающую влево ( шаг 2 ), затем нажмите правую кнопку, чтобы запустить моделирование в течение 2560 нс ( шаг 3 ) и, наконец, нажмите кнопку Zoom Fit кнопка ( шаг 4 ), чтобы масштабировать диапазон выходных данных моделирования по размеру окна:

Рисунок 4.22 - Результаты моделирования от начала до конца цикла

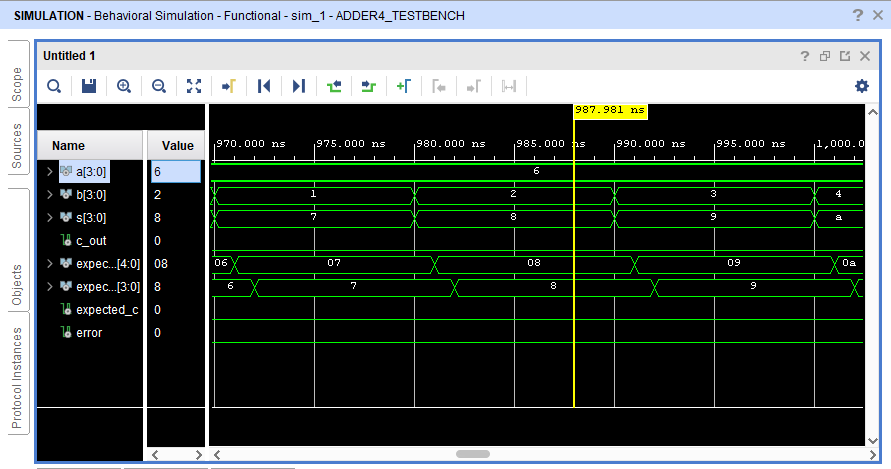

Вы можете использовать значки лупы, чтобы увеличить любую точку кривой и наблюдать за результатами каждой операции добавления, выполненной во время тестирования. Например, на следующем рисунке показано, что десятичные значения 6 и 2 были добавлены для получения результата 8 с переносом 0. Эти значения соответствуют ожидаемым значениям, что вызвало ошибку установить значение 0. Ошибка signal равно 0 для всех 256 тестовых примеров, что указывает на то, что наша логическая схема прошла все тесты:

Рисунок 4.23 - Увеличенное изображение результатов моделирования

- Закройте режим моделирования, нажав X синим цветом МОДЕЛИРОВАНИЕ полоса над графиком данных Нажмите ОК когда вас спросят, хотите ли вы закрыть симуляцию.

Пройдя поведенческое тестирование, мы определим сигналы ввода-вывода, используемые в проекте.

Определение сигналов ввода-вывода

Наш следующий шаг - подключить входы и выходы нашей схемы к аппаратным устройствам на плате Arty. Входами будут переключатели и кнопки на плате, а выходами - светодиоды.

Следующие шаги создадут файл ограничений, который описывает выводы ввода / вывода, которые мы будем использовать на устройстве FPGA, и функции, связанные с этими выводами на плате Arty. Файлы ограничений имеют расширение xdc:

- В разделе Источники во вложенном окне щелкните правой кнопкой мыши Ограничения и выберите Добавить источники… .

- В Добавить источники диалоговом окне убедитесь, что Добавить или создать ограничения выбран, затем нажмите Далее .

- В Добавить или создать ограничения в диалоговом окне нажмите Создать файл . .

- Введите имя файла Arty-A7-100.xdc (или Arty-A7-35.xdc если подходит для вашего устройства) и нажмите ОК .

- Нажмите Готово . чтобы отклонить Добавить или создать ограничения

- Разверните Ограничения исходное дерево и дважды щелкните Arty-A7-35.xdc .

- Digilent предоставляет предварительно заполненные файлы ограничений для плат Arty A7. Посетите https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc и скопируйте все содержимое окна браузера в окно редактора Arty-A7-35.xdc в Vivado. Если подходит для вашего устройства, используйте файл по адресу https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc вместо этого.

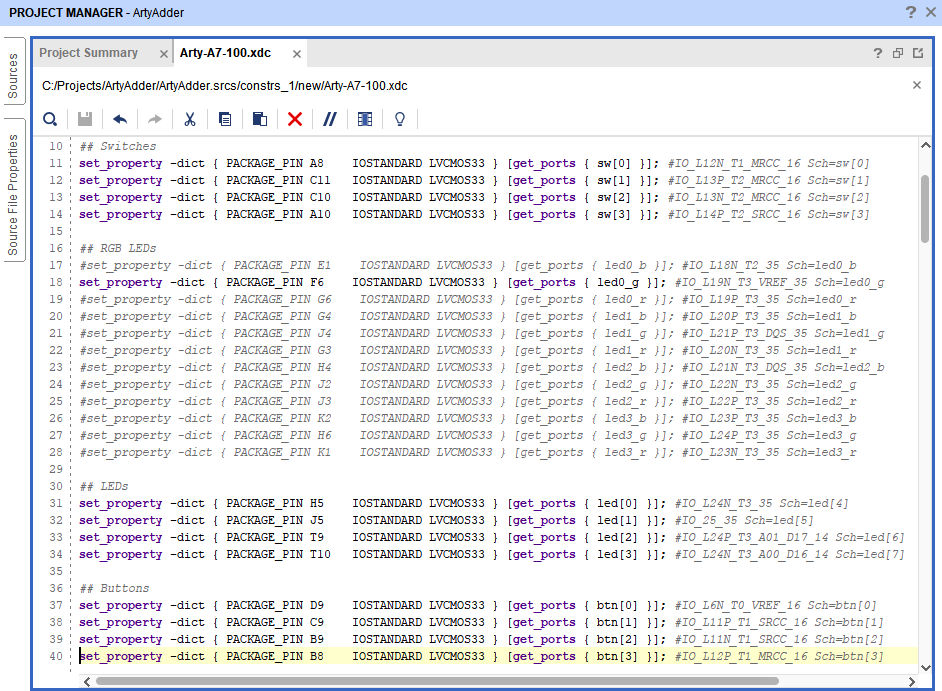

- Все контакты ввода-вывода закомментированы в файле ограничений путем раскомментирования соответствующих строк в файле путем удаления символа # в начале каждой строки. Мы будем использовать булавки, перечисленные в следующих разделах Arty- A7-100.xdc файл: Переключатели , RGB Светодиоды (но только led0_g , первый зеленый светодиод), светодиоды и кнопки . На следующем рисунке показаны эти строки после того, как они были раскомментированы:

Рисунок 4.24 - Окно редактора ограничений

В следующем разделе мы создадим файл VHDL верхнего уровня, который связывает код сумматора с устройствами ввода-вывода.

Создание файла VHDL верхнего уровня

Затем мы создадим файл VHDL верхнего уровня, который соединит наш 4-битный компонент сумматора с соответствующими сигналами ввода-вывода платы:

- В разделе Источники в дополнительном окне щелкните правой кнопкой мыши Источники дизайна . и выберите Добавить источники… .

- В Добавить источники в диалоговом окне убедитесь, что Добавить или создать источники дизайна выбран, затем нажмите Далее .

- В Добавить или создать источники дизайна в диалоговом окне нажмите Создать файл . .

- Введите имя файла vhdl и нажмите ОК .

- Нажмите Готово . чтобы закрыть Добавить или создать источники дизайна диалоговое окно, затем нажмите ОК в Определить модуль диалоговое окно и нажмите Да когда вас спросят, уверены ли вы, что хотите использовать эти

- Дважды щелкните vhdl . в разделе Источники дизайна . Удалите автоматически заполненное содержимое ArtyAdder.vhdl . окно редактора и введите следующий код в ArtyAdder.vhdl редактор:

- Загрузить стандартные библиотеки библиотеки IEEE; используйте IEEE.STD_LOGIC_1164.ALL; объект ARTY_ADDER - это порт (sw:в STD_LOGIC_VECTOR (3 вниз до 0); btn:в STD_LOGIC_VECTOR (3 вниз до 0); led:out STD_LOGIC_VECTOR (3 вниз до 0)); ARTY_ADDER; архитектура BEHAVIORAL для ARTY_ADDER - Ссылка на предыдущее определение 4-битного компонента сумматора ADDER4 - это порт (A4:в std_logic_vector (3 вниз до 0); B4:в std_logic_vector (3 вниз до 0); SUM4:вне std_logic_vector (3 вниз до 0); C_OUT4:из std_logic); конечный компонент; начало ADDER:карта портов ADDER4 (A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g); конечная архитектура BEHAVIORAL;

Этот код отображает имена сигналов для устройств ввода-вывода, названных в Arty-A7-100.xdc как sw (4 переключателя), btn (4 кнопки), светодиод (4 одноцветных светодиода) и led0_g (зеленый канал первого многоцветного светодиода) к ADDER4 входы и выходы.

Хотя VHDL не чувствителен к регистру, обработка xdc Файлы ограничений в Vivado чувствительны к регистру. Регистр, используемый в именах устройств ввода-вывода, определенных в xdc файл должен быть идентичным, если на него есть ссылка в файле VHDL. В частности, имена сигналов ввода-вывода в VHDL должны быть в этом файле в нижнем регистре, потому что в файле ограничений они указаны в нижнем регистре.

Теперь мы готовы синтезировать, реализовать и запрограммировать наш дизайн для платы Arty.

Синтез и реализация потока битов FPGA

Кроме того, вы можете выбрать Создать битовый поток . и Vivado выполнит все необходимые шаги, включая синтез, реализацию и генерацию битового потока, без дальнейшего вмешательства пользователя. Если произойдет фатальная ошибка, процесс остановится, и будут отображены сообщения об ошибках. Выполните следующие шаги, чтобы сгенерировать битовый поток:

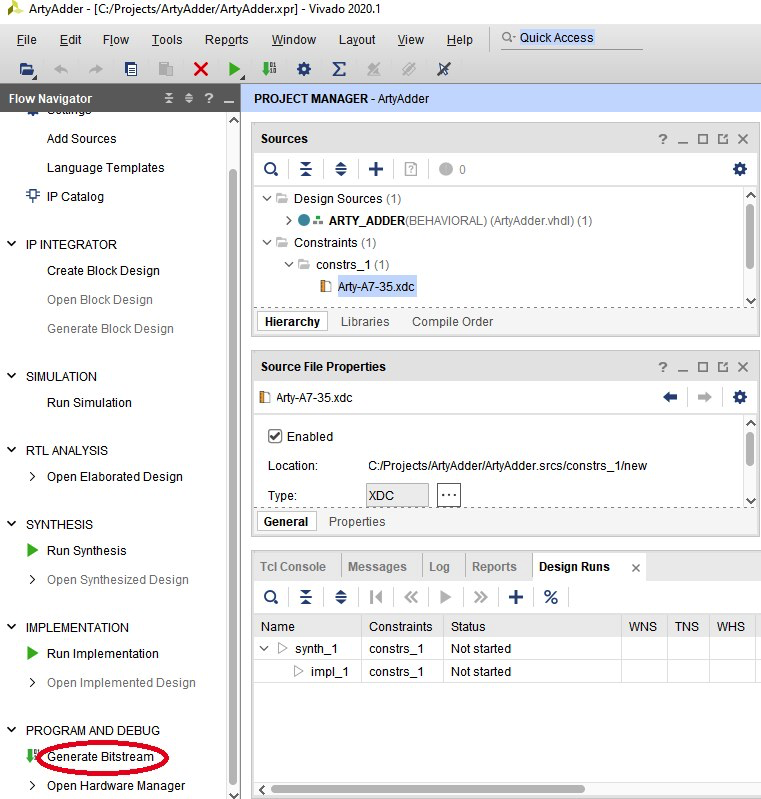

- Нажмите Создать битовый поток . для начала сборки Вас могут спросить, хотите ли вы сохранить текстовые редакторы. Нажмите Сохранить . . Вас могут проинформировать об отсутствии доступных результатов внедрения и спросить, можно ли начать синтез и реализацию. Нажмите Да . :

Рисунок 4.25. Выбор меню «Создать битовый поток»

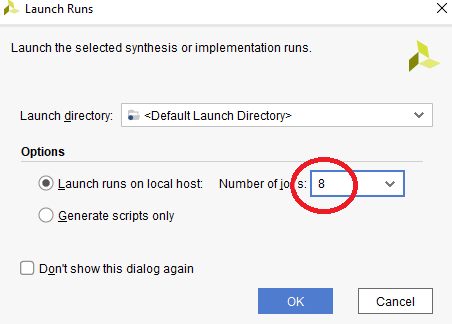

- запуски появится диалоговое окно. Вы можете выбрать значение для Количество заданий до количества ядер процессора в вашем компьютере. Использование большего количества ядер ускоряет процесс, но может привести к сбоям в работе вашего компьютера, если вы захотите продолжить его использование во время длительного процесса сборки. Нажмите ОК . чтобы начать сборку:

Рисунок 4.26. Диалоговое окно "Запуск запусков"

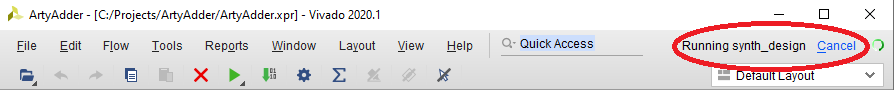

- В процессе сборки Vivado будет отображать статус в правом верхнем углу главного окна. При необходимости вы можете отменить процесс сборки, нажав Отмена . рядом с отображением статуса:

Рисунок 4.27. Отображение статуса компиляции

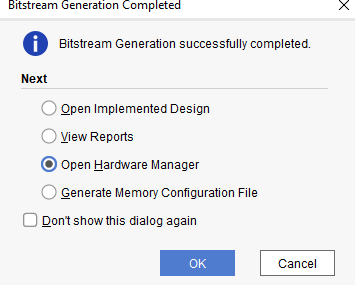

- Когда процесс сборки завершится (при условии отсутствия критических ошибок), появится сообщение Генерация битового потока завершена . диалог будет Хотя предлагаются и другие варианты, мы перейдем непосредственно к загрузке битового потока на плату Arty. Выберите Открыть диспетчер оборудования . и нажмите ОК :

Рисунок 4.28. Диалоговое окно "Генерация битового потока завершена"

Затем мы загрузим битовый поток в FPGA.

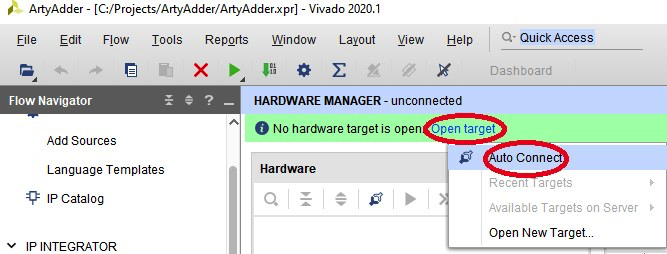

Рисунок 4.29. Выборы "Открыть цель" и "Автоматическое соединение"

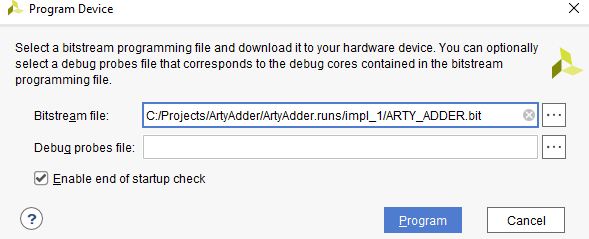

- Через несколько секунд Vivado должен указать, что плата подключена. Нажмите Запрограммировать устройство . чтобы загрузить битовый поток FPGA в Arty Вам будет предложено выбрать файл битового потока. Если вы использовали ту же структуру каталогов, что и в этом примере, файл будет расположен по адресу C:/ Projects / ArtyAdder / . ArtyAdder.runs / impl_1 / ARTY_ADDER.bit :

Рисунок 4.30 - Диалоговое окно "Программирование устройства"

- Нажмите Программа . загрузить программу на устройство FPGA и запустить ее

- Теперь вы можете протестировать работу программы с Arty I / O. Установите все четыре переключателя в положение выключено . положение (переместите переключатели к соседнему краю платы) и не нажимайте ни одну из четырех кнопок. Все четыре зеленых светодиода должны погаснуть.

- Если вы включите какой-либо отдельный переключатель или нажмете любую кнопку, должен загореться соответствующий зеленый светодиод. Включение любой комбинации переключателей при нажатии любого количества кнопок добавит соответствующие 4-битные числа и загорится светодиоды с сообщением Если есть перенос (например, включить SW3 и нажмите BTN3 одновременно) загорится зеленый светодиод переноса.

Выполняемый здесь процесс программирования сохранил программу в RAM FPGA. Если вы выключите и снова включите плату FPGA, вам нужно будет повторить процесс программирования, чтобы перезагрузить программу. Кроме того, вы можете сохранить файл конфигурации FPGA во встроенной флэш-памяти, как описано в следующем разделе.

Программирование потока битов во встроенную флэш-память

Чтобы настраивать FPGA каждый раз, когда на плату Arty подается питание, файл конфигурации FPGA должен быть сохранен во флэш-памяти на плате. Если установлена перемычка MODE, FPGA попытается загрузить файл конфигурации из встроенной флэш-памяти при включении питания. Эта память расположена в отдельной микросхеме рядом с ПЛИС Artix-7. Выполните следующие действия, чтобы запрограммировать файл конфигурации во флэш-память:

- Установите РЕЖИМ . перемычку на плате Arty, если она еще не вставлена

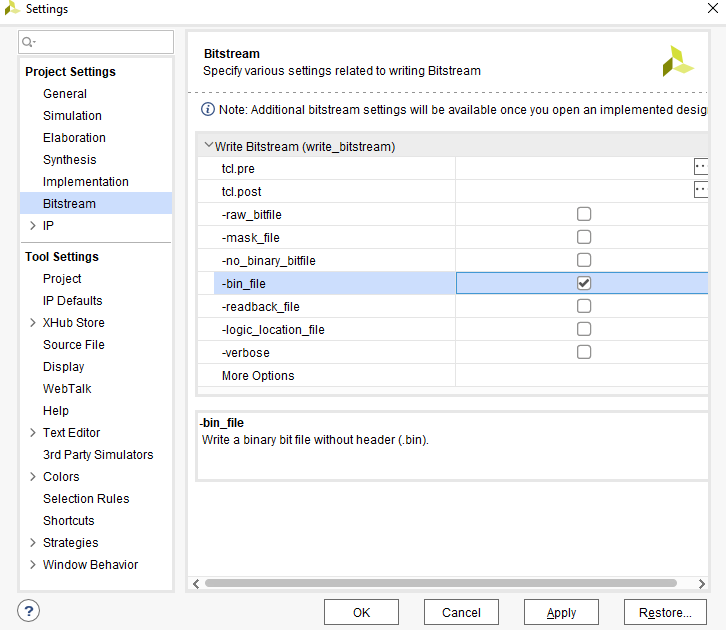

- Щелкните правой кнопкой мыши Создать битовый поток . и выберите Настройки битового потока… .

- В Настройках диалоговом окне установите флажок рядом с -bin_file и нажмите ОК :

Рисунок 4.31 - Диалог настроек битового потока

- В главном диалоговом окне Vivado нажмите Создать битовый поток . и повторить процесс генерации битового потока. Нажмите Отмена . когда генерация битового потока завершена диалог

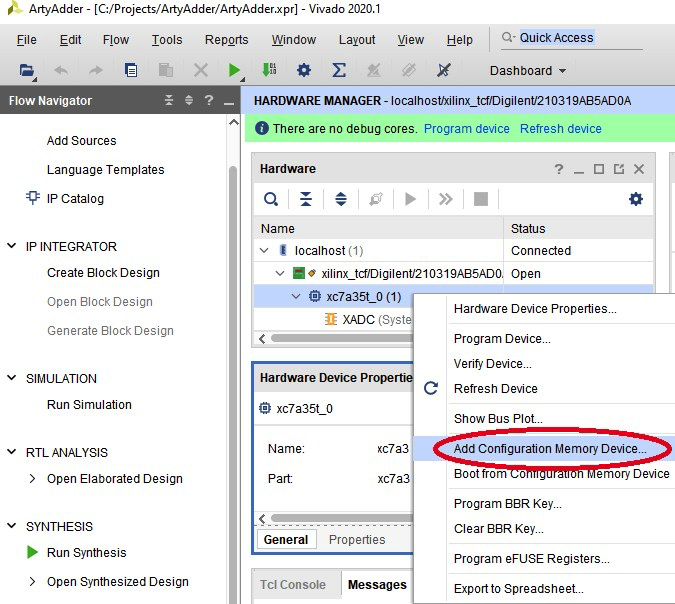

- В разделе Оборудование диалоговом окне щелкните правой кнопкой мыши номер детали FPGA ( xc7a100t_0 ) и выберите Добавить устройство памяти конфигурации… :

Рисунок 4.32. Пункт меню «Добавить устройство памяти конфигурации…»

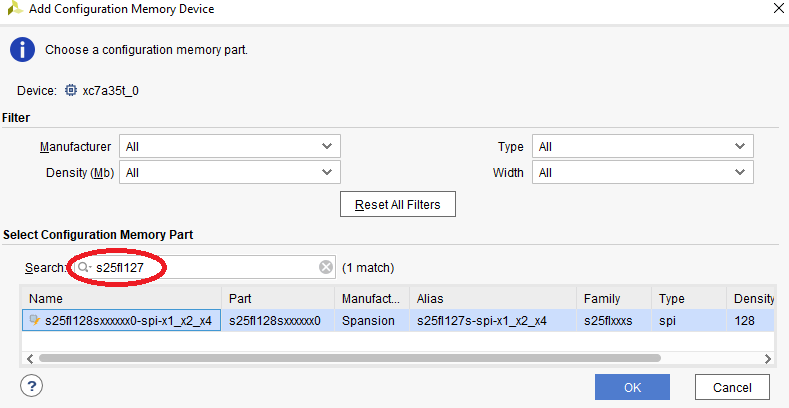

- Введите s25fl127 . в Поиск Должен появиться один совпадающий номер детали. Выберите деталь и нажмите ОК . :

Рисунок 4.33. Диалоговое окно "Добавить устройство памяти конфигурации"

- Появится диалоговое окно с вопросом Вы хотите сейчас запрограммировать устройство памяти конфигурации? Нажмите ОК . .

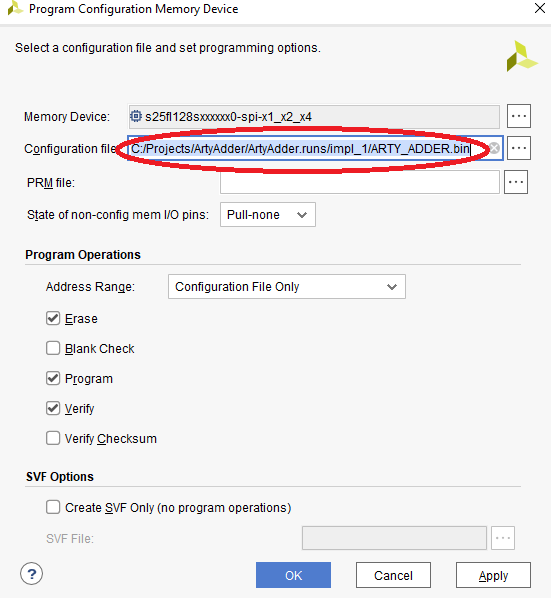

- Откроется Устройство памяти конфигурации программ . диалоговое окно с запросом имени файла конфигурации. Нажмите … кнопка справа от файла конфигурации и выберите C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin. Нажмите ОК . :

Рисунок 4.34. Диалоговое окно "Устройство памяти для конфигурации программы"

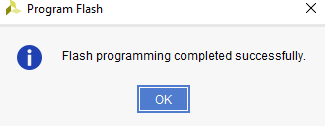

- Процесс программирования займет несколько секунд. После того, как файл был запрограммирован во флэш-память платы, вы должны получить сообщение об успешном завершении:

Рисунок 4.35. Диалоговое окно завершения программы Flash

После этого каждый раз, когда вы выключаете питание платы, загружается и запускается 4-битная программа сумматора. Программа долго загружается с настройками, которые мы использовали для загрузки файла конфигурации. Чтобы не ждать, пока ПЛИС загрузит программу, вы можете повысить скорость загрузки файла конфигурации, выполнив следующие шаги:

- Выберите Открытый синтезированный дизайн . в Flow Navigator .

- В главном меню Vivado выберите Инструменты / Редактировать свойства устройства… .

- В разделе Общие на вкладке установите Включить сжатие битового потока . на ИСТИНА .

- В Конфигурации на вкладке установите Скорость конфигурации (МГц) на 33, затем нажмите ОК .

- Снова сгенерируйте поток битов и запрограммируйте флеш-память, как описано. Вам нужно будет удалить устройство памяти конфигурации и снова добавить его, чтобы отобразить параметр для перепрограммирования.

- Закройте Оборудование . Менеджер .

- Отключите USB-кабель платы Arty и подключите его. Программа должна запускаться практически мгновенно при включении питания.

В этом разделе представлен пример простой комбинационной логики, взаимодействующей с сигналами на выводах ввода / вывода FPGA. Здесь мы хотели познакомить вас с Vivado

набор инструментов и продемонстрировать, как эти инструменты используются для выполнения полного цикла разработки ПЛИС.

Резюме

Эта глава началась с обсуждения эффективного использования ПЛИС в архитектурах встроенных систем реального времени и продолжилась описанием стандартных устройств ПЛИС и содержащихся в них низкоуровневых компонентов. Был представлен ряд языков проектирования FPGA, включая HDL, методы блок-схем и популярные языки программирования, такие как C / C ++. Был представлен план процесса разработки ПЛИС. Глава завершается полным примером цикла разработки ПЛИС, начиная с изложения требований и заканчивая функциональной системой, реализованной на недорогой плате для разработки ПЛИС.

Завершив эту главу, вы должны знать, как ПЛИС могут быть эффективно применены в архитектурах встроенных систем реального времени, и понимать компоненты внутри интегральной схемы ПЛИС. Вы узнали о языках программирования, используемых при разработке алгоритмов ПЛИС, этапах цикла разработки ПЛИС и понимаете последовательность этапов процесса разработки ПЛИС.

В следующей главе будет подробно рассмотрен процесс разработки FPGA, чтобы предоставить полный подход к архитектуре встроенных систем реального времени, содержащих FPGA. Также будет начата разработка прототипа высокопроизводительной встроенной системы - цифрового осциллографа, который послужит примером для следующих глав.

Перепечатано с разрешения Packt Publishing. Авторские права © 2021 Packt Publishing

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT).

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT). Связанное содержание:

- Встроенный дизайн с ПЛИС:аппаратные ресурсы

- Встроенный дизайн с ПЛИС:языки реализации

- Встроенный дизайн с ПЛИС:процесс разработки

- Инструменты с открытым исходным кодом помогают упростить программирование FPGA.

- Реализация алгоритмов с плавающей запятой в ПЛИС или ASIC.

- Использование ПЛИС для глубокого обучения

- Программные инструменты переносят код GPU на FPGA для приложений AI.

Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Что такое дизайн встроенной системы:этапы процесса проектирования

- Обработка 3D-печатных деталей ... мелками?

- Интервью с экспертом:главный технолог ANSYS по достижению успеха в 3D-печати из металла с помощью моделирования

- Превращение больших данных в интеллектуальные данные с помощью встроенного ИИ

- Проблемы реализации порта USB Type-C и проектные решения

- Ключевые отраслевые тенденции влияют на дизайн встраиваемых систем

- Платформа с открытым исходным кодом нацелена на Интернет вещей со встроенным Linux

- Clientron:многофункциональный POS-терминал со встроенным принтером

- Конструкторский комплект для измерения артериального давления с помощью оптического датчика

- Все вместе с добавками