Встроенный дизайн с FPGA:аппаратные ресурсы

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

1:аппаратные ресурсы (эта статья)

2:языки реализации

3:Процесс разработки

4:Создание проекта

5. Реализация

Адаптировано из книги Джима Ледина "Архитектура высокопроизводительных встраиваемых систем".

Разработка вашей первой программы FPGA

Эта глава начинается с обсуждения эффективного использования устройств FPGA во встроенных системах реального времени и продолжается описанием функциональных элементов, содержащихся в стандартных FPGA. Диапазон языков проектирования ПЛИС, включая Аппаратное обеспечение . Языки описания ( ЛПВП ), методы блок-схем и популярные языки программирования, включая C и C ++. Глава продолжается обзором процесса разработки ПЛИС и завершается полным примером цикла разработки ПЛИС, начиная с изложения системных требований и заканчивая функциональной системой, реализованной в недорогой плате для разработки ПЛИС.

После завершения этой главы вы узнаете, как ПЛИС могут применяться в архитектурах встроенных систем реального времени, и разберетесь в компонентах, составляющих интегральную схему ПЛИС. Вы познакомитесь с языками программирования, используемыми при разработке алгоритмов FPGA, и поймете последовательность шагов для разработки приложения на основе FPGA. Вы также должны будете проработать полный пример разработки FPGA на недорогой плате для разработки с использованием бесплатных программных инструментов FPGA.

В этой главе мы рассмотрим следующие темы:

- Использование ПЛИС во встроенных системах реального времени.

- Языки реализации FPGA

- Процесс разработки FPGA

- Разработка вашего первого проекта FPGA.

Технические требования

Файлы для этой главы доступны по адресу https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systems.

Использование ПЛИС во встроенных системах реального времени

Как мы видели в разделе Элементы FPGA раздел главы 1 , Создание высокопроизводительной архитектуры Встроенные системы , типичное устройство FPGA содержит большое количество таблиц поиска, триггеров, элементов блочного ОЗУ, фрагментов DSP и других компонентов. Хотя может быть полезно понять подробные возможности каждого из этих компонентов, такие проблемы не обязательно информативны в процессе разработки FPGA. Самым важным ограничением, которое следует иметь в виду, является то, что конкретный номер детали FPGA содержит конечное количество каждого из этих элементов, и проект не может выходить за эти пределы, если ориентирован на эту конкретную модель FPGA.

Вместо этого более продуктивно рассматривать процесс разработки FPGA с точки зрения требований к встроенной системе. Вы можете начать разработку проекта FPGA, ориентированного на произвольно выбранную модель FPGA. По мере продолжения разработки вы можете достичь предела ресурсов или определить функцию FPGA, которая требуется для проектирования, которой нет в текущей целевой FPGA. На этом этапе вы можете выбрать другую, более способную цель и продолжить разработку.

В качестве альтернативы, по мере того, как разработка проекта приближается к завершению, вы можете понять, что целевая FPGA, которую вы изначально выбрали, содержит чрезмерные ресурсы, и проект можно улучшить, выбрав меньшую FPGA, с потенциальными преимуществами с точки зрения более низкой стоимости, меньшего количества выводов, меньшего размера корпуса, и пониженное энергопотребление.

В любой из этих ситуаций, как правило, просто переключить целевую FPGA на другую модель в том же семействе. Инструменты разработки и артефакты дизайна, которые вы создали к этому моменту, должны быть полностью повторно использованы с новой целевой моделью FPGA. Если возникнет необходимость перейти на другое семейство ПЛИС от того же поставщика или на модель от другого поставщика, переход, вероятно, потребует дополнительных усилий.

Смысл этого обсуждения состоит в том, чтобы подчеркнуть, что не так важно идентифицировать конкретную модель FPGA в начале разработки высокопроизводительной встраиваемой системы. Вместо этого предварительные соображения должны быть сосредоточены на подтверждении решения об использовании ПЛИС как части проекта, а затем, если ПЛИС является лучшим подходом к проектированию, переходите к выбору подходящего поставщика ПЛИС и семейства устройств.

Примеры проектов в этой книге будут основаны на семействе инструментов разработки ПЛИС Xilinx Vivado. Хотя для разработки для некоторых семейств Xilinx FPGA необходимо приобрести лицензию Vivado, устройства FPGA в Artix-7, с которыми мы будем работать, поддерживаются Vivado бесплатно. Семейство ПЛИС Artix-7 сочетает в себе такие атрибуты, как высокая производительность, низкое энергопотребление и снижение общей стоимости системы. Подобные семейства устройств FPGA и наборы средств разработки доступны от других поставщиков FPGA.

Разработка ПЛИС - довольно сложный процесс, требующий различных типов анализа и ввода проектных данных. Чтобы избежать обсуждения этих тем на слишком абстрактном уровне и представить конкретные результаты в терминах рабочих примеров проектов, мы будем использовать Vivado на протяжении всей книги. Когда вы ознакомитесь с инструментами и методами, обсуждаемыми здесь, вы сможете применять их, используя аналогичные инструменты других поставщиков.

В следующих разделах будут обсуждаться некоторые ключевые отличительные особенности семейств ПЛИС и отдельных моделей внутри этих семейств, включая количество блочной ОЗУ, количество и типы доступных сигналов ввода-вывода, специализированные аппаратные ресурсы на кристалле и включение одно или несколько ядер аппаратного процессора в пакете FPGA.

Блокировка ОЗУ и распределенная ОЗУ

Заблокировать ОЗУ используется для реализации областей памяти в ПЛИС. Конкретная область памяти указывается в терминах ширины в битах (обычно 8 или 16 бит) и глубины, которая определяет количество ячеек для хранения в области памяти.

Общее количество блочной ОЗУ в ПЛИС обычно указывается в килобитах . ( КБ ). Объем доступной блочной ОЗУ варьируется в зависимости от семейств ПЛИС и моделей в одном семействе. Как и следовало ожидать, более крупные и дорогие детали обычно имеют большее количество ресурсов, которые можно использовать в качестве ОЗУ блока.

В ПЛИС Xilinx и, в разной степени, в ПЛИС других производителей, в дополнение к блочной ОЗУ доступна отдельная категория памяти, называемая распределенной ОЗУ. Распределенная оперативная память состоит из логических элементов, используемых в справочных таблицах, и перепрофилирует схемы этих устройств для формирования крошечных сегментов ОЗУ, каждый из которых содержит 16 бит. При необходимости эти сегменты можно объединить в блоки памяти большего размера.

Блочная RAM обычно используется для целей, традиционно связанных с RAM, таких как реализация кэш-памяти процессора или в качестве буфера для хранения данных ввода-вывода. Распределенная RAM может использоваться для таких целей, как временное хранение промежуточных результатов вычислений. Поскольку распределенная ОЗУ основана на схеме таблицы поиска, использование распределенной ОЗУ в проекте сокращает ресурсы, доступные для реализации логических операций.

Блочная RAM может иметь один порт или два порта. Однопортовая блочная ОЗУ представляет собой обычную схему использования процессора, который читает и записывает ОЗУ во время работы.

Двухпортовая блочная ОЗУ предоставляет два порта чтения / записи, оба из которых могут одновременно активно читать или записывать одну и ту же область памяти.

Двухпортовая блочная RAM идеально подходит для ситуаций, когда данные передаются между частями FPGA, работающими с разными тактовыми частотами. Например, подсистема ввода-вывода может иметь тактовую частоту в сотни МГц при получении входящего потока данных. Подсистема ввода-вывода записывает входящие данные в блочную RAM по мере их поступления через один из высокоскоростных каналов ввода-вывода FPGA. Отдельная подсистема в ПЛИС, работающая с другой тактовой частотой, может считывать данные из второго порта блочного ОЗУ, не мешая работе подсистемы ввода-вывода.

Блочная RAM также может работать в режиме первым пришел - первым обслужен . ( FIFO ) Режим. В примере входящего потока последовательных данных подсистема ввода-вывода может вставлять слова данных в FIFO по мере их поступления, а подсистема обработки может считывать их в том же порядке. Блочная RAM в режиме FIFO выдает сигналы, указывающие, заполнен ли FIFO, пуст, почти полон или почти пуст. Определения почти полный и почти пустой зависят от разработчика системы. Если вы назначите почти пустой Это означает, что в FIFO осталось менее 16 элементов, тогда вы можете быть уверены, что каждый раз, когда FIFO не показывает, что он почти пуст, вы можете прочитать 16 элементов без дополнительных проверок доступности данных.

При использовании блочной RAM в режиме FIFO жизненно важно, чтобы логика, вставляющая элементы в FIFO, никогда не пыталась писать, когда FIFO заполнен, а логическое чтение из FIFO никогда не пыталось читать, когда FIFO пуст. Если произойдет одно из этих событий, система либо потеряет данные, либо попытается обработать неопределенные данные.

Контакты ввода-вывода FPGA и связанные с ними функции

Поскольку ПЛИС предназначены для использования в высокопроизводительных приложениях, их выводы ввода-вывода, как правило, способны реализовать множество стандартов высокоскоростного ввода-вывода. Во время реализации проекта с помощью набора инструментов разработки FPGA разработчик системы должен выполнять задачи, которые включают в себя назначение функций определенным контактам в пакете FPGA и настройку каждого из этих контактов для работы с соответствующим стандартом интерфейса. Необходимо выполнить дополнительные шаги, чтобы связать входные и выходные сигналы в коде модели FPGA с правильными выводами пакета.

На уровне выводов отдельные сигналы ввода / вывода могут быть несимметричными или дифференциальными.

несимметричный сигнал ссылается на землю. Традиционная транзисторно-транзисторная логика ( TTL ) и Дополнительный металл-оксид-полупроводник ( CMOS ) цифровые сигналы работают в диапазоне 0-5 В постоянного тока относительно земли.

Современные ПЛИС обычно не поддерживают устаревший диапазон сигналов 5 В постоянного тока, а вместо этого поддерживают сигналы TTL и CMOS, работающие в пониженном диапазоне напряжений, тем самым снижая энергопотребление и повышая скорость. TTL низкого напряжения ( LVTTL ) сигналы работают в диапазоне 0–3,3 В постоянного тока. КМОП низкого напряжения ( LVCMOS ) сигналы можно выбрать с помощью сигнальных напряжений 1,2, 1,5, 1,8, 2,5 и 3,3 В. Эти типы сигналов называются LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25 и LVCMOS33. Доступны и другие высокопроизводительные несимметричные типы сигналов, включая High-Speed Transceiver Logic . ( HSTL ) и Терминированная логика серии заглушек ( SSTL ).

Несимметричные сигналы широко используются для низкочастотных целей, например, для считывания входов кнопок и освещения светодиодов. Несимметричные сигналы также используются во многих протоколах низкоскоростной связи, таких как I2C и SPI. Важным недостатком несимметричных сигналов является то, что любой шум, связанный с проводами и дорожками печатной платы, несущими сигнал, может повредить вход приемника. Эту проблему можно существенно уменьшить за счет использования дифференциальной сигнализации.

Для самых высоких скоростей передачи данных предпочтительным подходом является дифференциальная сигнализация.

Дифференциальные сигналы используйте пару контактов ввода / вывода и подавайте противоположные сигналы на два контакта.

Другими словами, на один вывод подается более высокое напряжение, а на другой вывод - более низкое напряжение, чтобы представить бит данных 0, а напряжения на выводах меняются местами, чтобы представить бит 1. Дифференциальный приемник вычитает два сигнала, чтобы определить, равен ли бит данных 0 или 1. Поскольку два провода или дорожки, несущие дифференциальный сигнал, физически расположены очень близко друг к другу, любой шум, который входит в один из сигналов, будет соединяться с другим. очень похожим образом. Операция вычитания удаляет подавляющую часть шума, обеспечивая надежную работу при гораздо более высоких скоростях передачи данных, чем несимметричные сигналы.

Ряд стандартов дифференциальных сигналов поддерживается стандартными ПЛИС. Определено несколько дифференциальных версий HSTL и SSTL с различными уровнями сигнального напряжения для каждой.

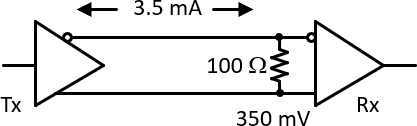

Дифференциальная сигнализация низкого напряжения ( LVDS ) был введен в качестве стандарта в 1994 году и продолжает использоваться во множестве приложений. Передатчик сигналов LVDS вырабатывает постоянный ток 3,5 мА и переключает направление тока, протекающего через резистор в приемнике, для изменения состояния, представляющего значения данных 0 и 1, как показано на Рис. 4.1 :

Рисунок 4.1. Интерфейс LVDS

В связи LVDS, как и в других стандартах дифференциальной и несимметричной сигнализации, важно, чтобы полное сопротивление тракта связи между передатчиком и приемником близко соответствовало оконечному сопротивлению, которое в случае LVDS составляет 100 Ом. Если импеданс канала связи не соответствует оконечному сопротивлению, в линии могут возникать отражения, препятствующие надежному приему данных.

Импеданс пар дорожек дифференциального сигнала является функцией геометрии дорожек пары и их отношения к плоскости заземления. Как мы увидим в главе 6 , Разработка схем с помощью KiCad , несложно спроектировать печатные платы, удовлетворяющие требованиям стандартов высокоскоростной дифференциальной сигнализации.

Специализированные аппаратные ресурсы

ПЛИС обычно включают в себя набор выделенных аппаратных ресурсов для функций, которые обычно требуются и которые либо более эффективно реализованы аппаратно, а не с использованием синтезированных функций ПЛИС, либо не могут быть реализованы с помощью компонентов ПЛИС. Вот некоторые примеры этих ресурсов:

- Интерфейсы с внешней динамической RAM ( DRAM ) для хранения большого количества этих интерфейсов, как правило, поддерживает общий стандарт DRAM, такой как DDR3.

- Аналого-цифровые преобразователи.

- Цепи фазовой автоподстройки частоты, используемые для генерации нескольких тактовых частот.

- Цифровая обработка сигналов умножение-накопление ( MAC ) оборудование.

Эти аппаратные ресурсы позволяют разрабатывать сложные системы с широкими возможностями. Для таких функций, как операция MAC, предоставляется специальное оборудование, поскольку производительность оборудования значительно выше, чем у синтезированных эквивалентных функций с использованием логических ресурсов FPGA.

Ядра процессора

Некоторые семейства FPGA включают ядра аппаратных процессоров с целью объединения пиковой скорости выполнения программного обеспечения с преимуществами производительности алгоритмов, реализованных на FPGA. Например, семейство Xilinx Zynq-7000 объединяет аппаратный процессор ARM Cortex-A9 вместе с традиционной структурой FPGA.

Проекты FPGA, не требующие аппаратного процессора, могут реализовать процессор, использующий ресурсы FPGA, называемый программным процессором . . Программные процессоры легко настраиваются, хотя, как правило, они не могут соответствовать производительности процессора, реализованного на оборудовании.

В следующем разделе будут представлены основные языки программирования и методы ввода данных, используемые для разработки алгоритмов FPGA.

Перепечатано с разрешения Packt Publishing. Авторские права © 2021 Packt Publishing

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT).

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT). Связанное содержание:

- Инструменты с открытым исходным кодом помогают упростить программирование FPGA.

- Реализация алгоритмов с плавающей запятой в ПЛИС или ASIC.

- Использование ПЛИС для глубокого обучения

- Программные инструменты переносят код GPU на FPGA для приложений AI.

- ПЛИС вытесняют ASIC в системе ADAS на базе зрения Subaru Eyesight.

- Как ПЛИС на основе флэш-памяти упрощают требования функциональной безопасности.

- Воспользуйтесь преимуществами мгновенного включения ПЛИС

- Конфигурация FPGA с использованием высокоскоростной флеш-памяти NOR

- Как технология FPGA развивается, чтобы соответствовать новым системным требованиям среднего уровня.

Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Как избежать дорогостоящих сюрпризов при проектировании подключаемого оборудования

- Что такое дизайн встроенной системы:этапы процесса проектирования

- Упрощение разработки IoT с помощью Eclipse IoT

- Разработка конечных автоматов с помощью разработки через тестирование

- Превращение больших данных в интеллектуальные данные с помощью встроенного ИИ

- Cypress:ModusToolbox Suite упрощает проектирование Интернета вещей

- Решетка:MachX03D FPGA повышает безопасность за счет аппаратных возможностей корневого доверия

- Конструкторский комплект для измерения артериального давления с помощью оптического датчика

- Java 9 — улучшение «Попробуйте с ресурсами»

- Все вместе с добавками