Встроенный дизайн с FPGA:языки реализации

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

Примечание редактора. По мере появления передовых алгоритмов для разработки интеллектуальных продуктов разработчики часто сталкиваются с трудностями при реализации встроенных систем, способных удовлетворить связанные с этими алгоритмами требования к обработке. ПЛИС могут обеспечивать требуемую производительность, но проектирование с использованием ПЛИС долгое время считалось ограниченным компетенцией экспертов по программированию ПЛИС. Однако сегодня наличие более мощных ПЛИС и более эффективных сред разработки сделало разработку ПЛИС широко доступной. В этом отрывке, главе 4 из книги «Архитектура высокопроизводительных встроенных систем», автор предлагает всесторонний обзор устройств FPGA, языков реализации и процесса разработки FPGA, а также подробное пошаговое руководство по началу реализации FPGA самостоятельно. дизайн. Полный отрывок представлен в следующих частях:

1:аппаратные ресурсы

2:Языки реализации (эта статья)

3:Процесс разработки

4:Создание проекта

5. Реализация

Адаптировано из книги "Архитектура высокопроизводительных встроенных систем" Джима Ледин.

Языки реализации FPGA

Реализация проекта FPGA в конечном итоге сводится к использованию одного или нескольких языков, подобных программному программированию, для определения функциональности устройства.

Традиционными языками, используемыми для разработки FPGA, являются VHDL и Verilog.

Инструменты разработки FPGA текущего поколения обычно поддерживают оба этих языка вместе с возможностью определять конфигурации системы с помощью методов блок-схем. Некоторые наборы инструментов также поддерживают определение функциональности FPGA с использованием традиционных языков программирования C и C ++.

VHDL

Язык описания оборудования VHSIC ( VHDL ), где VHSIC означает Очень . Высокоскоростная интегральная схема , имеет синтаксис, напоминающий язык программирования Ada. VHDL был разработан под руководством Министерства обороны США с 1983 года.

Как и Ada, VHDL имеет тенденцию быть довольно многословным и жестко структурированным. С точки зрения языка программирования, VHDL строго типизирован. Язык содержит предопределенный набор базовых типов данных, в основном логических, битовых, bit_vector, символьных, строковых, целых, реальных, временных и массивов. Все остальные типы данных определены в терминах базовых типов.

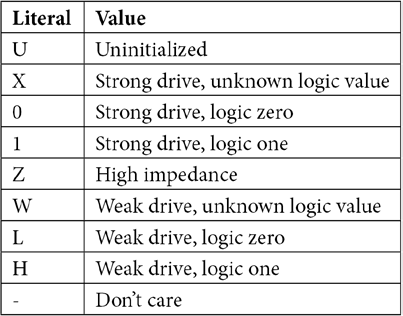

Набор библиотек VHDL был определен Институтом инженеров по электротехнике и радиоэлектронике . ( IEEE ) и формализована как стандарт IEEE 1164, Многозначная логическая система для Взаимодействие модели VHDL . Эти библиотеки определяют набор логических значений, которые будут использоваться в языке VHDL. Эта библиотека включает тип с именем std_logic, который представляет 1-битный сигнал. Логические значения в типе std_logic представлены символьными литералами, показанными в следующей таблице:

«Сильные» значения 0 и 1 на предыдущем рисунке представляют сигналы, переведенные в заданное двоичное состояние. «Слабые» сигналы представляют собой сигналы, передаваемые по шине с несколькими драйверами, где любой драйвер может заявить о себе на шине, подавляя другие драйверы. Значение Z представляет собой КМОП-выход в состоянии с высоким импедансом, когда вместо перевода шины в состояние 0 или 1 выход фактически отключается от шины и не управляет ею вообще. Состояние U представляет значения по умолчанию для всех сигналов. При выполнении моделирования схемы будет обнаружен любой сигнал в состоянии U, что, вероятно, указывает на непреднамеренное использование неинициализированного значения. Состояние X связано с проводами, которые не имеют управляющих выходов. Состояние - представляет входы, которые не используются, и поэтому не имеет значения, в каком состоянии они находятся.

Проектирование схем VHDL обычно начинается с импорта библиотек IEEE 1164 с помощью следующих операторов:

библиотека IEEE;

используйте IEEE.std_logic_1164.all;

Мы будем использовать VHDL в нашем примере проекта позже в этой главе. Это не означает сильное предпочтение VHDL перед Verilog. Оба языка описания аппаратного обеспечения полностью способны представить практически любую конструкцию, которая может быть синтезирована для ПЛИС.

Verilog

Язык описания оборудования Verilog ( HDL ) был представлен в 1984 году и стал стандартизирован как IEEE 1364 в 2005 году. В 2009 году стандарт Verilog был объединен с SystemVerilog стандарт для производства стандарта IEEE 1800-2009. SystemVerilog содержит обширные возможности для выполнения проверки системы в дополнение к конструктивным особенностям аппаратного обеспечения, представленным в Verilog.

Verilog был разработан, чтобы напоминать язык программирования C, включая аналогичный приоритет операторов и использование некоторых из тех же ключевых слов потока управления, включая if, else, for и while.

Verilog использует концепцию провода . для представления состояний сигнала. Значение сигнала может принимать любое из значений 0, 1, безразлично (x) или высокое сопротивление (z), а также может иметь сильный или слабый мощность сигнала.

И VHDL, и Verilog определяют языковые подмножества, которые можно использовать для разработки логических схем. Эти подмножества называются синтезируемыми языковые подмножества. Дополнительные языковые функции помимо синтезируемых подмножеств доступны для поддержки таких задач, как моделирование схем. Позже в этой главе мы увидим пример этого.

Несинтезируемые языковые конструкции, как правило, ведут себя больше как традиционные языки программирования. Например, несинтезируемый цикл for выполняет итерацию по блоку кода последовательно указанное количество раз, как в обычном языке программирования. С другой стороны, синтезируемый цикл for становится эффективно развернутым для создания коллекции реплицированных аппаратных конструкций, которые выполняются параллельно, представляя каждую итерацию цикла.

Блок-схемы

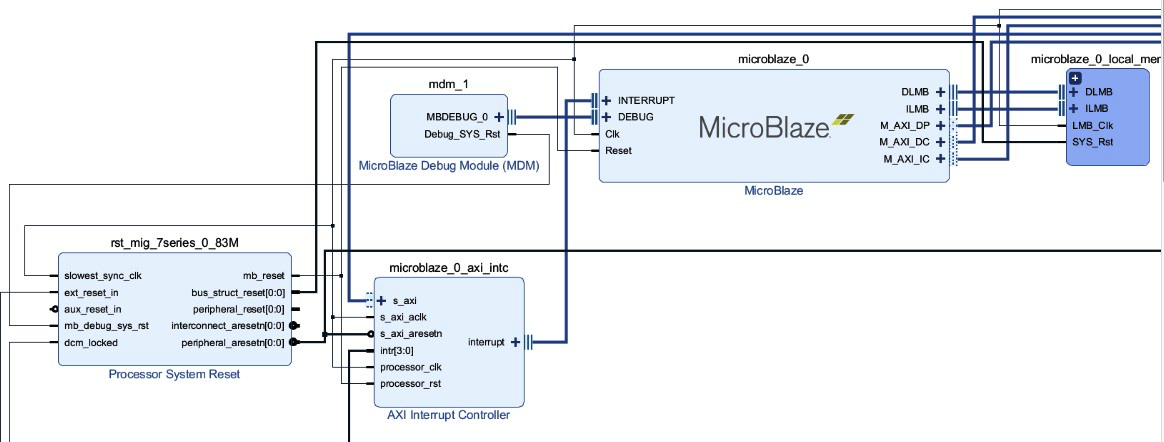

На уровне абстракции, превышающем текстовые HDL, современные комплекты инструментов разработки FPGA поддерживают быструю настройку системных проектов, включающих сложные логические компоненты, такие как микропроцессоры и сложные устройства ввода-вывода, с использованием формата блочной структуры. Рисунок 4.2 представляет собой пример части блок-схемы для проекта Xilinx FPGA, включающего программный процессор MicroBlaze:

щелкните, чтобы просмотреть изображение в полном размере

Рисунок 4.2 - Блок-схема микропроцессора MicroBlaze soft

Процессор MicroBlaze представляет собой процессорное ядро, поставляемое с набором инструментов Xilinx Vivado для использования в проектах FPGA в семействах процессоров, включая Artix-7.

Хотя использование блок-схем обеспечивает визуально интуитивно понятный способ организации создания экземпляров и взаимосвязей сложных логических элементов в проекте FPGA, важно помнить, что за диаграммой инструмент разработки генерирует код VHDL или Verilog для определения компонентов и их соединения. Блок-схема - это просто пользовательский интерфейс для управления конфигурацией этих компонентов.

После разработки блок-схемы вы можете изучить сгенерированный код HDL, который будет содержаться в файлах, связанных с проектом. На диаграмме Рисунок 4.2 , из диаграммы создается файл с именем design_1_microblaze_0_0_stub.vhdl. Этот файл начинается со следующего кода VHDL:

библиотека IEEE;

используйте IEEE.STD_LOGIC_1164.ALL;

entity design_1_microblaze_0_0 есть

Порт (

Clk:в STD_LOGIC;

Сброс:в STD_LOGIC;

Прерывание:в STD_LOGIC;

Interrupt_Address:в STD_LOGIC_VECTOR (от 0 до 31);

Interrupt_Ack:out STD_LOGIC_VECTOR (от 0 до 1);

Instr_Addr:out STD_LOGIC_VECTOR (от 0 до 31);

Instr:в STD_LOGIC_VECTOR (от 0 до 31);

Этот код начинается со ссылки на стандартную библиотеку IEEE 1164, а затем определяет интерфейс для процессора MicroBlaze, который предоставляет ожидаемые от микропроцессора сигналы, включая системные часы, сброс, запрос прерывания и входные вектора прерывания; выходы подтверждения прерывания и адреса команд; и шина для инструкций, извлеченных из памяти.

Этот код использует типы данных библиотеки IEEE 1164 для однобитовых сигналов (STD_LOGIC) и для многобитовых сигналов шины (STD_LOGIC_VECTOR).

Код в листинге определяет интерфейс процессора MicroBlaze, но не содержит определения HDL самого процессора. Сложные конструкции HDL для таких компонентов, как микропроцессоры, считаются ценной интеллектуальной собственностью . ( IP ), и коммерческие организации, которые разрабатывают эти конструкции, часто принимают меры, чтобы гарантировать, что они не будут использоваться без соответствующего лицензирования. Когда поставщики распространяют IP для использования своими клиентами, он может быть предоставлен в скомпилированном формате, непрозрачном для конечных пользователей. Это позволяет пользователям включать IP в свои проекты, но они не могут исследовать HDL, использованный для его разработки. Это концептуально похоже на разработчиков программного обеспечения, которые выпускают библиотеку в скомпилированной форме, но не предоставляют исходный код.

C / C ++

Ряд поставщиков предлагают программные инструменты, которые переводят традиционные языки программирования высокого уровня, часто C и C ++, в код HDL для использования при разработке FPGA. Этот подход может быть привлекательным, если у вас есть сложный алгоритм на C или C ++, который вы хотели бы ускорить в реализации FPGA. Эти инструменты также позволяют разработчикам программного обеспечения, знакомым с C / C ++, немедленно приступить к реализации кода для использования FPGA без необходимости изучения одного из HDL.

Хотя инструменты разработки FPGA для этих языков высокого уровня способны значительно оптимизировать результирующую реализацию алгоритма кода C / C ++ на FPGA, все же есть некоторая несогласованность в том, что модель выполнения C / C ++ включает в себя последовательное выполнение операторов, в то время как собственная среда FPGA состоит из параллельных аппаратных компонентов. Конструкция FPGA, являющаяся результатом кода C / C ++, обычно напоминает набор конечных автоматов, которые управляют последовательным выполнением операций, определенных в операторах языка программирования. В зависимости от наличия возможностей для параллельного выполнения в коде C / C ++ реализация FPGA может обеспечить значительное повышение производительности по сравнению с запуском того же кода на традиционном процессоре.

В современных наборах средств разработки FPGA все методы реализации FPGA, описанные в этом разделе (VHDL, Verilog, блок-схемы и C / C ++), при необходимости могут быть объединены в единую конструкцию. Из-за этого один член команды может предпочесть работать в VHDL, а другой использует Verilog. Могут быть причины, по которым руководство проекта не поощряет использование нескольких HDL в рамках одного проекта, но сами языки без проблем функционируют вместе в едином дизайне. Одна из причин, по которой руководитель проекта может пожелать избежать использования нескольких HDL, заключается в том, что для продолжения работы в будущем потребуется участие разработчиков, владеющих обоими языками.

Точно так же можно определить высокоуровневую архитектуру проекта в терминах блок-схемы, а затем реализовать детальную функциональность подсистемы, используя выбранный HDL. В том же дизайне также можно интегрировать HDL, созданный с помощью алгоритма C / C ++. Архитекторы и разработчики встроенных систем должны внимательно рассмотреть последствия и выбрать соответствующий метод реализации для каждой части проекта FPGA.

В следующем разделе будут представлены этапы стандартного процесса разработки ПЛИС.

Перепечатано с разрешения Packt Publishing. Авторские права © 2021 Packt Publishing

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT).

Джим Ледин является генеральным директором Ledin Engineering, Inc. Джим является экспертом в области проектирования, разработки и тестирования встроенного программного и аппаратного обеспечения. Он также имеет опыт оценки кибербезопасности встроенных систем и тестирования на проникновение. У него есть степень бакалавра наук. степень в области аэрокосмической техники Университета штата Айова и степень магистра наук степень в области электротехники и вычислительной техники Технологического института Джорджии. Джим является зарегистрированным профессиональным инженером-электриком в Калифорнии, сертифицированным специалистом по безопасности информационных систем (CISSP), сертифицированным этическим хакером (CEH) и сертифицированным тестером на проникновение (CPT). Связанное содержание:

- Встроенный дизайн с ПЛИС:аппаратные ресурсы

- Инструменты с открытым исходным кодом помогают упростить программирование FPGA.

- Реализация алгоритмов с плавающей запятой в ПЛИС или ASIC.

- Программные инструменты переносят код GPU на FPGA для приложений AI.

- ПЛИС вытесняют ASIC в системе ADAS на базе зрения Subaru Eyesight.

- Как ПЛИС на основе флэш-памяти упрощают требования функциональной безопасности.

- Воспользуйтесь преимуществами мгновенного включения ПЛИС

- Конфигурация FPGA с использованием высокоскоростной флеш-памяти NOR

- Как технология FPGA развивается, чтобы соответствовать новым системным требованиям среднего уровня.

Чтобы получить больше информации о Embedded, подпишитесь на еженедельную рассылку Embedded по электронной почте.

Встроенный

- Что такое встроенное системное программирование и его языки

- Что такое дизайн встроенной системы:этапы процесса проектирования

- Превращение больших данных в интеллектуальные данные с помощью встроенного ИИ

- Проблемы реализации порта USB Type-C и проектные решения

- Ключевые отраслевые тенденции влияют на дизайн встраиваемых систем

- Ускоритель FPGA для камер MIPI со встроенным зрением

- Clientron:многофункциональный POS-терминал со встроенным принтером

- Конструкторский комплект для измерения артериального давления с помощью оптического датчика

- Дебют ПЛИС оборонного уровня с ранним доступом

- Все вместе с добавками